赛题一:利用AI技术优化模拟信号源

随着芯片设计和制造技术的进步,越发复杂的测试需求对测试系统提出了更高的挑战,提供更精准可靠的信号源是其中之一。在构建信号源的过程中,我们需要对信号源生成电路做各种调试,确认其达到精确可靠的要求。新兴的的AI技术为我们提高信号源信号质量打开了全新的思路。我们在探索将现有硬件系统搭配AI技术得以实现性能突破的可能。

要求:

基于参考硬件电路的D/A构建频率可调高精度正弦模拟信号源。

利用参考硬件电路的A/D测量该信号源的关键指标。

利用AI技术,不改变信号源硬件实现和测试条件,对该信号源的非线性指标进行优化。

测量并对比分析优化后的结果。

参赛者通过设计AI模型完成主要指标的训练、优化,并提交优化结果,包括但不限于:

标注:

1报名参赛的前三十只队伍凭预研方案(PPT),将获得泰瑞达提供的一套参考硬件电路 (A/D+D/A)预研方案中包括但不限于:

2参赛者利用提供的参考硬件电路搭建系统硬件平台,并配合MCU/ARM/DSP/FPGA/PC等实现。

评分标准:

优化后信号源的指标(不同频率下);

AI模型的性能指标;

预研方案,优化报告的质量;

源代码的编码质量;

提供原始数据加分;

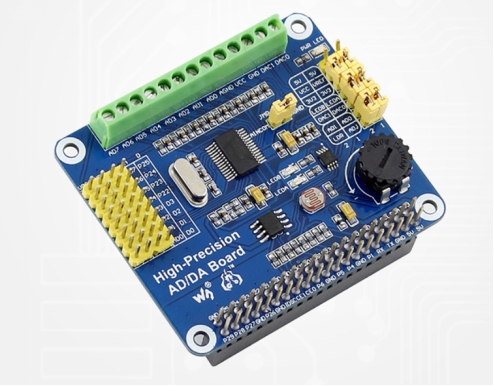

附录1: 参考硬件电路

https://www.waveshare.net/shop/High-Precision-AD-DA-Board.htm

AD: ADS1256, 24-bit 8 Channel, data rate up to 30ksps

DA: DAC8552, 16-bit 2 Channel, settling time 10us

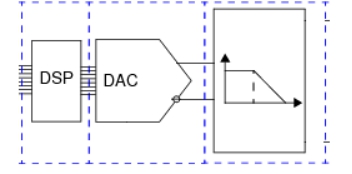

附录2:可参考的基于D/A的信号源的电路

图中的DSP可以是DSP,也可以是MCU/ARM/DSP/FPGA/PC。

赛题二:程序语言-UML时序智能生成器

在集成电路行业,随着芯片设计和制造技术的进步,程序规模日益增大,越来越多的项目采用高速迭代的敏捷开发模式,由此为开发及测试人员带来项目周期短,复杂度高的挑战。如果设计一个智能分析器,以自动化分析程序的逻辑及执行流程,并生成UML的时序图,以图形的方式直观表现出程序架构,就可以有效地提高代码分析的效率,缩短项目迭代周期。

要求:

参赛者可自行决定要使用的开发语言;

参赛者可选择C#或JAVA程序语言作为分析对象;

可以使用开源的第三方库;

最终生成UML时序图;

以下是经过简化的输入及输出件样本,仅供参考。

http://cpipc.acge.org.cn/sysFile/downFile.do?fileId=c707b40c175e45c2ba3b587da6444a13

一份文件,程序中只有函数,表达式,没有流程控制语句和全局对象的定义。(参照:Sample_Level1-3.zip/Level1Sample文件夹)

一份文件,程序中有if else和 loop 等流程控制语句,并且有嵌套调用。(参照:Sample_Level1-3.zip/Level2Sample文件夹)

多份文件,每份文件中定义一个Class,程序中有if else和 loop 等流程控制语句,并且有嵌套调用。(参照:Sample_Level1-3.zip/Level3Sample文件夹)

评分标准:

http://cpipc.acge.org.cn/sysFile/downFile.do?fileId=5760be77b09e4f31b9c3cbbdcfd8f730

输出要求:

奖项设置:

一等奖(一支队伍) 奖金10,000人民币,公司暑期实习,优先录用

二等奖(三支队伍) 奖金5,000人民币每队,优先录用

赛题专项答疑:

Email地址:contest.china@teradyne.com

企业命题答疑请注明:

华为杯、参赛题目编号、参赛队伍信息(学校,队伍编号)、联系方式 (姓名,email地址,联系电话等)、问题描述

申请赛题一的参考硬件电路板请注明:

请在邮件中标注邮寄信息包括:学校名称,参赛队长姓名、联系电话、配送地址