赛题一:主动降噪(ANC)降噪滤波器设计及实现

描述及要求:

- 软硬件实现ANC降噪滤波器,支持多 Ref MIC ,多Err MIC(>=1)的ANC;

- 支持FF/FB/Hybrid(FF&FB)模式;

- ANC降噪滤波器工作在192kHz上;

- ANC降噪滤波器用Verilog HDL实现。

评审得分点:

- 声学建模方案清晰合理;

- ANC降噪滤波器系数训练方案清晰;

- 输出多mic降噪与单mic降噪效果对比;

- 设计的ANC降噪滤波器具有较大的降噪深度和和降噪带宽;

- ANC降噪滤波器对多种噪声均具备一定的鲁棒性。

输出要求:

- 算法模型的设计文档与代码,C/C++/Matlab代码不限

- 详细设计文档和逻辑Verilog HDL代码;

- 有验证数据及波形对比截图。

赛题二:主动降噪(ANC)外围低延时升降采样滤波器设计及实现

描述及要求:

- 软硬件实现ANC外围低延时升降采样滤波器;

- ANC方案支持数字或模拟micphone;

- ANC低延时升降采样滤波器用Verilog HDL实现;

评审得分点:

- ANC通路底噪低于-100dBV;

- Analogue->ADC->SRC->ANC CORE(direct through FF Filters@192kHz)->SRC->DAC-> Analogue不高于13us。

输出要求:

- 算法模型的设计文档与代码,C/C++/Matlab代码不限;

- 详细设计文档和逻辑代码;

- 有验证数据及波形对比截图。

赛题三:逻辑实现高性能NTT(数论变换)多项式乘法

描述及要求:

- 基于格理论的(全)同态加密算法的基本操作会涉及维数较大的整系数多项式的乘法,快速NTT算法可以提升多项式乘法的计算性能;

- 利用NTT算法实现

上的多项式乘法,其中n=256,q=3329;

上的多项式乘法,其中n=256,q=3329;

- NTT串行和并行实现方式二选一,综合频率不低于200MHz,工艺不限;

- NTT串行实现逻辑门数(不包含memory面积)不超过90KGE,NTT并行实现逻辑门数(不包含memory面积)不超过1400KGE,Memory可以使用寄存器搭建;

- NTT串行实现Cycles数不超过1024,NTT并行实现Cycles数不超过8;

评审得分点:

- 功能正确,实现符合题目要求;

- 需要有资源、面积、性能和功耗评估结果;

- 符合题目要求的基础上,性能越高,得分越高;

- 有考虑硬件攻击,如侧信道、故障注入等可加分;

输出要求:

1. 算法模型设计文档和算法模型代码;(C\matlab等不限)

2. 详细设计文档和逻辑代码、软件代码;

3. 算法实现合理性分析文档;

4. EDA验证报告;

赛题四:逻辑实现超低面积超低功耗带防护的AES算法

描述及要求:

- 采用Verilog实现超低面积超低功耗带防护的AES算法,工作时钟频率40MHz以上。

- AES算法模块支持常见的ECB加解密/CBC加解密/CMAC运算模式,输入数据只支持以Byte为单位,不支持以bit为单位,数据大小端不做要求;

- AES算法模块支持128bit/192bit/256bit密钥长度,不同密钥长度可通过配置选择;

- AES算法模块具有全面防御常见的侧信道(如CPA等)及错误注入(如DFA等)攻击的能力;

- 一轮AES运算采用4拍完成时:AES算法模块占用的逻辑门数不可超过20kGE。SMIC40nm工艺下RTL前仿功耗不大于0.6mw(40MHZ),其它工艺其它频率按工艺收益比例进行折算即可,并在设计文档中给出分析说明。一轮AES运算也可以采用4拍以上完成,此时性能、面积和功耗需要按比例折算。

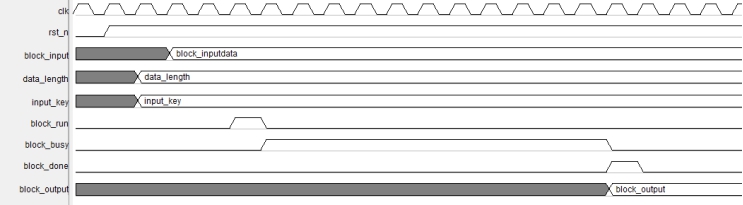

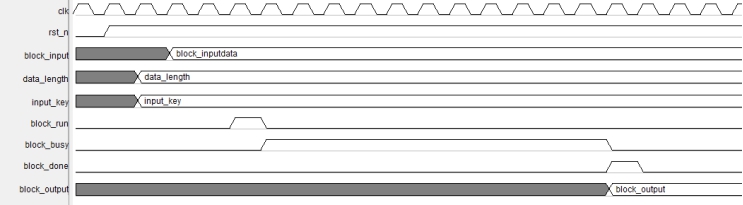

- 模块接口按照分组计算的方式实现,模块的接口可参考以下方式,实际实现时可根据具体实现进行增加或删减;

Input clk,

Input rst_n,

Input block_input,(位宽为一个输入分组长度,例如AES为128bit分组)

Input block_run,

Input data_length,(位宽32bit,验证最大10MB)

Input input_key,(位宽为输入密钥长度)

Output block_done,

Output block_output,(位宽为一个输出分组长度)

Output block_busy

评审得分点:

1.实现算法功能正确,满足题目要求;

2.设计方案文档描述清晰,模块功能划分合理;

3.代码简洁,可维护性好;

4.防攻击方案设计合理有效,防攻击效果越好,得分越高;

5.文档中要求明确的对面积和功耗优化的措施说明,优化措施越有效,模块面积越小,功耗越低,得分越高;

6.要求有完备的验证方案和验证用例;

输出要求:

1.算法模型代码及文档;(C\matlab等不限)

2.详细设计文档和逻辑代码;

3.输出验证用例、验证数据和波形截图;

赛题五:逻辑实现超高性能的SM4-GCM算法

描述及要求:

- 采用Verilog实现超高性能的SM4-GCM算法,明密文数据运算时平均运算性能达到80bit/cycle;AAD数据长度及IV长度不做要求,AAD数据长度可以为0,IV长度可以简化为96bit;

- SM4-GCM算法模块支持常见的SM4-GCM运算模式(要求GCTR和GHASH并行计算)和GHASH运算模式,输入数据只支持以Byte为单位,不支持以bit为单位,数据大小端不做要求;

- SM4-GCM模块内部包含多个运算单元,在SM4-GCM模块顶层需要完成对多个运算单元的调度逻辑;

- 设计时需要关注模块的面积、性能和功耗的平衡;

评审得分点:

1.实现算法功能正确,满足题目要求;

2.设计方案文档描述清晰,模块功能划分合理;

3.代码简洁,可维护性好;

4.文档中要求明确说明对多个运算核心的调度策略,调度方式越优化,得分越高;

5.在满足性能要求的前提下,模块面积越小,运算核心数量越少,功耗越低,可综合频率越高,得分越高;

6.文档中要求明确的对面积和功耗优化的措施进行说明,优化措施越有效,得分越高;

7.要求有完备的验证方案和验证用例;

输出要求:

1.算法模型代码及文档;(C\matlab等不限)

2.详细设计文档和逻辑代码;

3.输出验证用例、验证数据和波形截图;

赛题六: 小面积/低功耗TRNG熵源设计以及实现。

描述及要求:

- 熵源类型不限;

- 实现方式不限,数字或模拟电路均可以;

- 要求熵源面积/功耗尽量小:以SMIC-40nm工艺为例,数字熵源面积小于2000um2,模拟熵源面积小于6000um2,数字/模拟熵源的前仿功耗要求小于0.2mW;其他工艺请按工艺系数进行折算;

- 说明熵源的随机性原理,最好能对熵源进行建模;

评审得分点:

- 熵源熵值高,满足0.997的要求;

- PPA要求:面积小/功耗低;

- 实现简单,采用数字/模拟电路设计;

- 熵源建模能够从理论模型说明随机性来源,并证明熵值满足大于0.997;

输出要求:

- 熵源算法设计文档以及熵源建模文档;

- 详细设计文档以及逻辑代码。

赛题七: 基于ARM TrustZone架构的系统安全增强设计方案

描述及要求:

- 权限隔离是一种重要的安全防护手段,例如ARM TrustZone技术,将SOC分为安全和非安全两种权限空间。

- 实现一个满足ARM TrustZone要求的SOC系统具备安全和非安全权限的隔离能力。在此基础上,设计一种系统安全增强方案进一步提升安全世界的安全性;

- SOC中至少包含CPU(例如RISC-V)、总线、DMA、SRAM和一个外设接口(例如UART),其他组件可选,不做强制要求;

- 题目中未明确要求的,不做强制要求。

评审得分点:

- 正确设计满足ARM TrustZone规范要求的SOC系统,实现权限之间的隔离;

- 设计的SOC安全架构方案合理,可有效增强TrustZone安全世界的安全性;

- 设计方案清晰正确,对实现方式和性能进行详细分析;

- 提供功能、性能仿真报告,每个组件功能正确;

输出要求:

- 设计方案说明书;

- RTL代码 (Verilog或者VHDL);

- 功能、性能仿真报告。

赛题八:硬件实现超低功耗乘法器

描述及要求:

1. 采用Verilog实现低功耗无符号算术乘法器,要求乘法器位宽64bit。

2.乘法器不可以使用*实现

3.乘法器内部可插拍。

4.逻辑门不大于25Kgate

5.不要求在FPGA器件或ASIC器件等载体上实现,能通过综合、仿真验证即可;

评审得分点:

1.符合要求的基础上,功耗越低,得分越高。S40nm工艺下RTL前仿功耗不大于0.2mw(13MHZ),其它工艺按工艺收益比例进行折算即可。

2.实现乘法器的面积越小,得分越高。

3.需要说明所设计方案的优点和亮点,有资源、功耗仿真结果。

输出要求:

1.详细设计文档和逻辑代码;

2.实现合理性分析文档,需要着重说明低功耗设计思路;

赛题九:超高性能非对称算法RSA/ECC硬件实现

描述及要求:

- verilog实现RSA模幂/ECC点乘算法, RSA、ECC任选一种即可。RSA算法位宽支持典型位宽512/1024/2048/3072/4096bit,ECC算法支持典型位宽128/256/384/521bit;

- 要求硬件实现模幂/点乘;

- 在400MHz下,RSA2048指数2048bit运算性能不低于1000次/秒;ECC256点乘平均性能不低于2万次/秒;其他位宽、频率下性能按照比例折算;

- 实现频率、工艺、结构不做要求;逻辑面积不大于1000K gate,不包含memory面积。

- 对硬件主被动攻击安全性不做要求;

评审得分点:

1.RSA/ECC功能正确,EDA仿真通过,满足题目要求;

2.方案和实现文档描述清晰,硬件实现结构合理;

3.实现性能满足题目要求;

4.给出面积、频率;

5.有功耗评估结果;(此项为加分项,不做统一要求)

6.可具备加解密/签名验签能力。(此项为加分项,不做统一要求)

输出要求:

1.总体设计方案以及理论分析文档;

2.详细设计文档和逻辑代码、软件代码;

3.功能仿真报告。

作品提交要求:

由于华为赛题的专项奖是线下评审,没有答辩环节,除按竞赛组委会要求提交PPT外,还需按华为赛题要求提供文档和代码。如果是硬件作品,需提供照片或视频,含竞赛组成员合影。

华为专项奖设置:

华为公司为选作华为赛题的前15名赛队设立华为专项奖,获奖赛队可同时参评竞赛组委会设立的其它竞赛奖。

华为专项奖一等奖5队,每队奖金1万元,

华为专项奖二等奖10队,每队奖金0.5万元。

华为命题专家咨询邮箱:wangbo24@hisilicon.com

上的多项式乘法,其中n=256,q=3329;

上的多项式乘法,其中n=256,q=3329;