华为赛题专项奖设置:

华为企业命题专项奖专门用于奖励选择华为企业命题的赛队,华为企业命题专项奖是初赛奖,由企业专家评出。入围决赛的参赛队伍继续参加大赛决赛奖项评比,与初赛奖项互不冲突。

华为专项奖设:

特等奖 2队,每队奖金2万元,合计4万元。

一等奖 5队,每队奖金1万元,合计5万元。

二等奖 12队,每队奖金0.5万元,合计6万元。

华为赛题咨询答疑:

华为公司王老师,电子邮箱:wangbo24@hisilicon.com

华为赛题文档下载:

https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=1d9420897ad2485395a0ffe3a64bd2fc

华为赛题视频讲解

【2023年中国研究生创“芯”大赛-华为企业命题讲解】

https://www.bilibili.com/video/BV1i24y177K9/?share_source=copy_web&vd_source=731983d24066c046753f8a80d7ad6bd5

赛题一:24~29.5G毫米波PA设计

描述及要求(基础):

评审得分点:

输出要求:

赛题二:高精度PhaseShifter芯片设计

描述及要求:

评审得分点:

输出要求:

赛题三:低功耗高精度ADC设计

描述及要求:

1.输入信号带宽:>100K

2.有效分辨率(ENOB): >16bit

3.功耗:<2mW

5.输入信号幅度:1Vpp

6.架构:不限

7.工艺:建议使用标准CMOS工艺

8.温度范围:−20℃至+85℃

9.供电电压:随选定工艺而定

评审得分点:

1.思路正确,根据性能、功耗的要求要有合理的架构选型分析;

2.在满足指标要求的情况下FOM越高,得分越高。FOM超过185dB可获得额外加分;

3.需要有文档,说明各个子电路性能指标的分解依据,子电路结构的选择依据等;

4.各个子模块的功耗、噪声和非线性等用饼状图给出占比分析;

5.校准算法选择及有效性分析是加分项;

6.查询业界典型产品和paper的指标,分析差距存在的原因,和可能的改进方向;

输出要求:

1.系统模型或电路模型;

2.详细分析设计文档;

3.电路原理图仿真验证数据;

赛题四:LDPC编解码模块设计

描述及要求:

点击图标下载文件:LDPC编解码模块设计.rar

评审得分点:

输出要求:

赛题五:基于非线性PA(power amplifier)的预失真补偿模块设计

描述及要求:

点击图标下载文件:PA_model.rar

评审得分点:

输出要求:

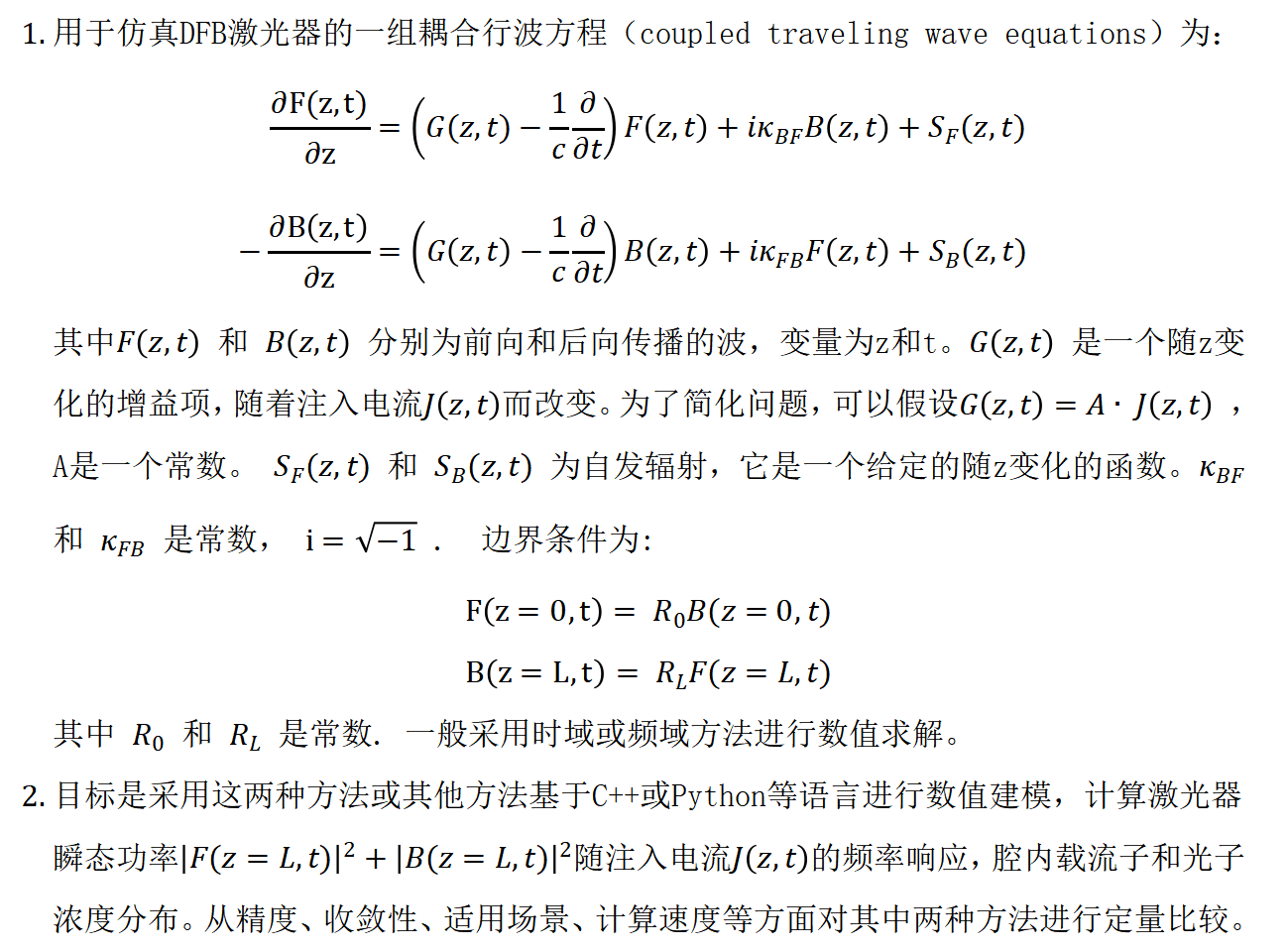

描述及要求:

评审得分点:

输出要求:

描述及要求(基础):

描述及要求(加分):

评审得分点:

输出要求:

赛题八:片上全集成Tsensor设计

背景介绍:

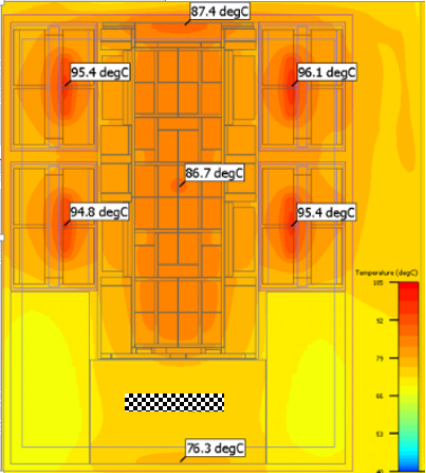

Tsensor(温度传感器)可集成在芯片内部,用于实现高精度Die内节温检测,在DIE上合理分布放置Tsensor可以得到DIE上的热力云图。Tsensor不断输出带有温度信息的二进制码值给SOC,芯片系统利用码值进行OTP(过热保护)/DVFS(动态电压频率调整)等控制。

题目描述及要求:

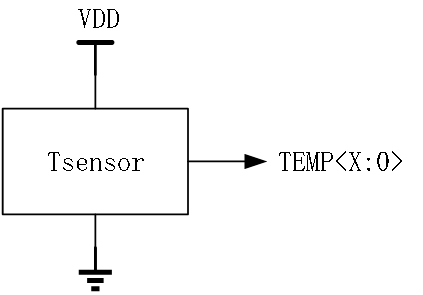

设计一个片上全集成Tsensor,输入信号仅提供电源(VDD),输出信号为可表征温度信息的数字信号(TEMP<X:0>),如下图所示。

主要指标的基本要求如下表所示,对于温度检测精度/吞吐率/功耗三项的性能得分详见评分标准表格。

|

指标名 |

基础要求 |

备注 |

|

温感单元 |

不使用BJT |

- |

|

温度检测范围 |

-40℃~125℃ |

- |

|

温度检测精度 |

≤±1℃ |

输出码值计算温度值与温度设定值间的偏差 |

|

吞吐率 |

≥10K sps |

输出数字码值刷新率 |

|

功耗 |

≤0.6mW |

包含所有电路(温感单元及检测电路) |

系统设计及仿真要求:

交付件要求:

评分标准:

|

类别 |

评分标准 |

最高分值 |

|

详细设计报告 |

1、系统框图清晰; |

15 |

|

前仿真报告 |

1、仿真用例对系统&模块指标覆盖率; |

15 |

|

指标达成度 |

温度检测精度 Accuracy≤±0.5℃:50分 |

50 |

|

功耗 |

10 |

|

|

吞吐率 1Ksps≤fs<10Ksps :5分 |

10 |

赛题九:可配置SAR ADC设计

题目描述:

模式一:6位模式的采样率不低于200MS/s。输入信号差分幅度Vppd=2*LVCC,LVCC为core device的标准电源电压。输入信号频率为奈奎斯特频率正弦波下,信噪失真比(SNDR)不低于35dB。输入信号源为理想信号源+100ohm输出阻抗。

模式二:8位模式采样速率为6位的1/4。输入信号差分幅度Vppd=2*LVCC,LVCC为core device的标准电源电压。输入信号频率为奈奎斯特频率正弦波下,信噪失真比(SNDR)不低于46dB。输入信号源为理想信号源。输入信号源为理想信号源+100ohm输出阻抗。

输出要求:

评分标准:

|

类别 |

评分标准 |

分值 |

|

详细设计报告 |

1、系统框图清晰; |

15 |

|

前仿真报告 |

1、仿真用例对系统&模块指标覆盖率; |

15 |

|

Schematic和tb数据库 |

|

10 |

|

指标达成度 |

6位模式下的速度fs fs < 200M: 0 200M ≤ fs < 300M: 10+10*(fs-200M)/100M fs > 300M: 20 |

20 |

|

6位模式下精度为SNDR SNDR < 35dB: 0 35dB≤SNDR < 37.85dB: 5+1.75*(SNDR - 35) SNDR ≥ 37.85 : 10 |

10 |

|

|

8位模式下精度SNDR SNDR < 46dB: 0 46dB≤SNDR < 49.9dB: 5+1.28*(SNDR – 46) SNDR≥ 49.9dB : 10 |

10 |

|

|

6位模式FoM FoM > 156fJ/conv.-step : 0 15.6fJ/conv.-step <FoM < 156fJ/conv.-step : (156 – FoM)/140.4*10 FoM < 15.6fJ/conv.-step: 10 |

10 |

|

|

8位模式FoM FoM > 156fJ/conv.-step : 0 15.6fJ/conv.-step <FoM < 156fJ/conv.-step : (156 – FoM)/140.4*10 FoM < 15.6fJ/conv.-step: 10 |

10 |

赛题十:高效定点乘法器设计

背景介绍:

|

被乘数 |

|

|

X3 |

X2 |

X1 |

X0 |

|

乘数 |

|

* |

Y3 |

Y2 |

Y1 |

Y0 |

|

|

|

|

X3Y0 |

X2Y0 |

X1Y0 |

X0Y0 |

|

|

|

X3Y1 |

X2Y1 |

X1Y1 |

X0Y1 |

|

|

|

X3Y2 |

X2Y2 |

X1Y2 |

X0Y2 |

|

|

|

X3Y3 |

X2Y3 |

X1Y3 |

X0Y3 |

|

|

|

|

X3Y3 |

… |

X1Y0+X0Y1 |

X0Y0 |

|||

图1:4*4的乘法器实现过程

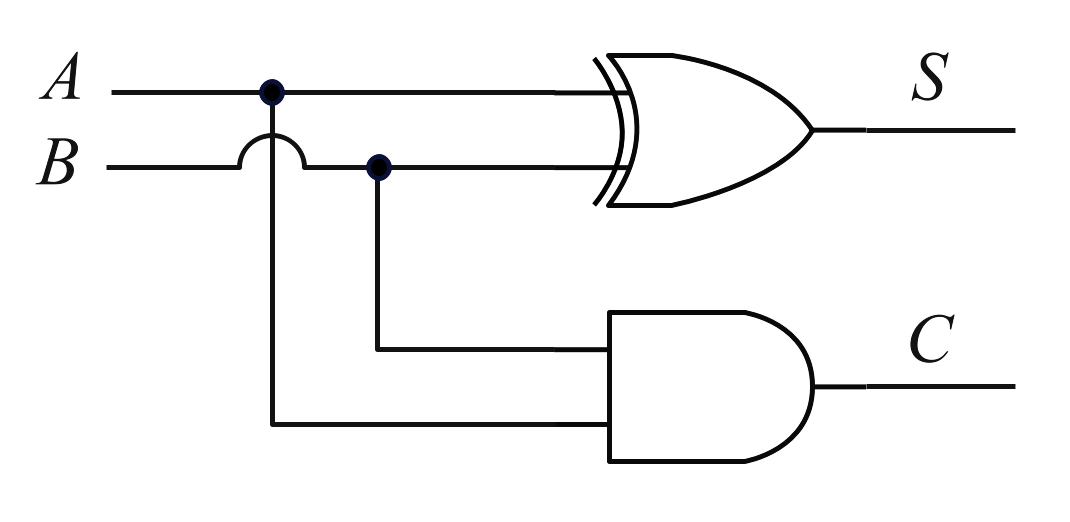

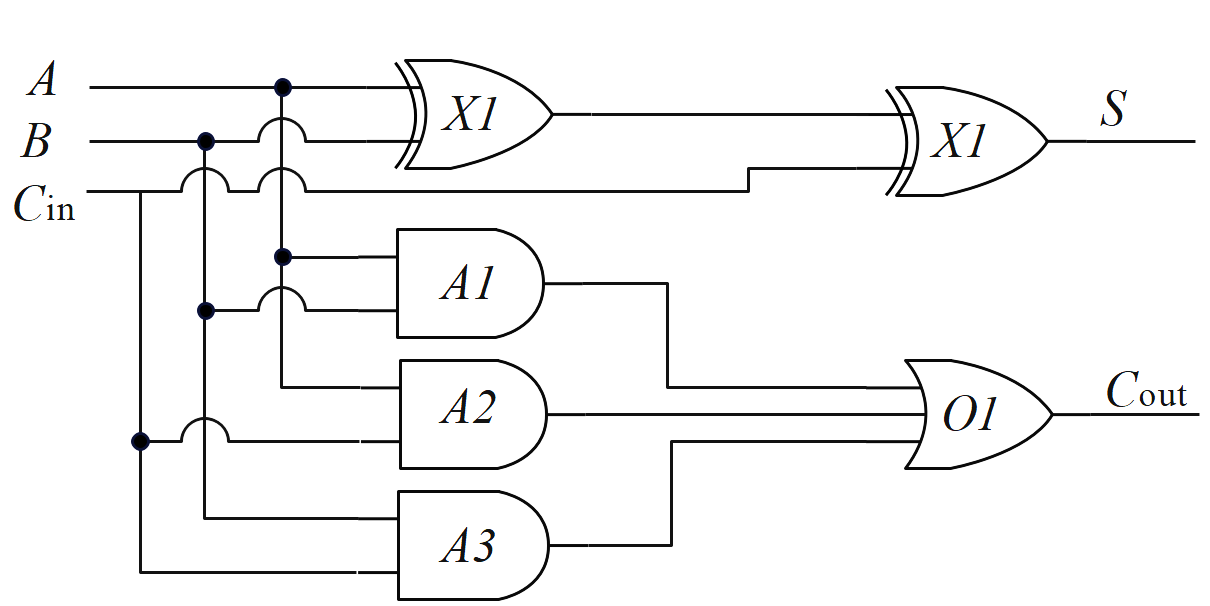

3.对于一般的阵列乘法器,X, Y两数相乘,同一权重(同一行上的部分积)需要进行压缩操作,将多个数据压缩到一个。即每一列的加法进位输入依赖于前一列的进位输出,这需要用到半加器或者全加器 ,其电路实现和真值表如图2和图3所示。

|

A |

B |

Carry |

Sum |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

图2:半加器逻辑实现和真值表

|

A |

B |

Cin |

Cout |

S |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

图3:全加器逻辑实现和真值表

4.评判一个定点乘法器实现的优劣,除了运算结果必须正确,还需要评估以下指标:

5.前人对乘法器做了很多优化,其中较为常见的是乘数编码和加法树压缩。乘数编码的目的是减少部分积的个数并降低加法树的深度,减少硬件资源使用。加法树压缩的目的是加快加法树的化简过程,减少硬件资源使用。两种方法的目的都是为了优化乘法器的实现过程,缩短关键路径,降低资源消耗。下面分别举例两种优化算法。

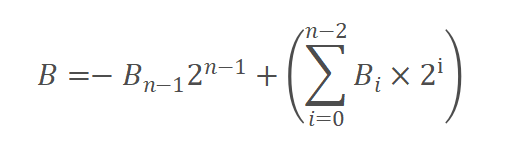

乘数编码有多种方案 ,其中booth编码最为常见,这里以基4booth算法举例,其原理如下:

对于N比特数B来说:

基4 Booth乘法器的基系数为:

|

Bi+1 |

Bi |

Bi-1 |

-2Bi +1+ Bi + Bi -1 |

部分积操作 |

|

0 |

0 |

0 |

+0 |

0 |

|

0 |

0 |

1 |

+1 |

A |

|

0 |

1 |

0 |

+1 |

A |

|

0 |

1 |

1 |

+2 |

2A |

|

1 |

0 |

0 |

-2 |

-2A |

|

1 |

0 |

1 |

-1 |

-A |

|

1 |

1 |

0 |

-1 |

-A |

|

1 |

1 |

1 |

-0 |

0 |

图4:基4 Booth真值表

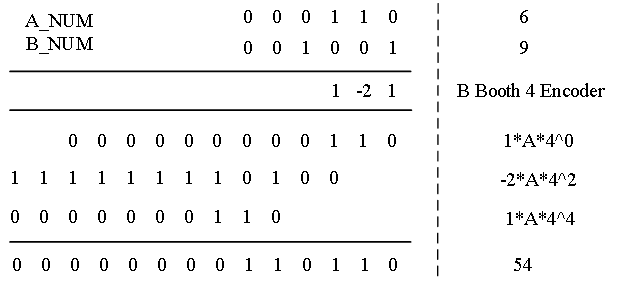

以7*9为例说明基4 Booth乘法器实现过程:

图5:基4 Booth乘法器实现过程

加法树的压缩:部分积的压缩则采用进位保留加法器的原理,使用进位保留加法器对部分积进行逐级压缩,直到最后压缩成只剩下两个部分积,即全加器的进位输出和模2和输出。以三个部分积压缩过程为例:首先将3个部分积压缩成两个部分积,然后再与下一个部分积组成新的一组,进行3:2压缩,直至最后压缩成2个部分积,具体过程如图 5所示。需要说明的是,进位保留的压缩方式是串行进行的。即对于N个部分积,需要N-2次压缩才能完成,即需要N-2级全加器。

加法树的压缩有多种方式,其中Wallace压缩是最为常见,以图一所示4*4的乘法过程举例Wallace压缩原过程其中红色数据用全加器处理,绿色数据采用半加器处理。

第一次压缩:

|

|

|

|

X3 |

X2 |

X1 |

X0 |

|

|

|

* |

Y3 |

Y2 |

Y1 |

Y0 |

|

|

|

|

X3Y0 |

X2Y0 |

X1Y0 |

X0Y0 |

|

|

|

X3Y1 |

X2Y1 |

X1Y1 |

X0Y1 |

|

|

|

X3Y2 |

X2Y2 |

X1Y2 |

X0Y2 |

|

|

|

X3Y3 |

X2Y3 |

X1Y3 |

X0Y3 |

|

|

|

第一次用两个半加器分别对X1Y2 和X0Y3 ,X2Y2+X1Y3进行处理,得到如下的部分积结果。

|

|

X3Y2 |

X3Y1 |

X3Y0 |

X2Y0 |

X1Y0 |

X0Y0 |

|

|

X2Y3 |

b1[0] |

X2Y1 |

X1Y1 |

X0Y1 |

|

|

X3Y3 |

b1[1] |

b0[1] |

b0[0] |

X0Y2 |

|

|

其中b0[0]为X1Y2 + X0Y3 的求和值,b1[0]为X1Y2 + X0Y3的进位值;b0[1]和b1[1]分别为对应X2Y2+X1Y3的求和值与进位值。

第二次压缩:

|

X3Y3 |

c3[0] |

c2[0] |

c1[0] |

X2Y0 |

X1Y0 |

X0Y0 |

|

c3[1] |

c2[1] |

c1[1] |

c0[1] |

c0[0] |

X0Y1 |

|

图6:Wallace压缩流程

其中c0[0]为X1Y1 + X0Y2的求和值,c1[0]为该半加器进位值;c0[1]为X3Y0 + X2Y1+ b0[0]的求和值,c1[1]为该全加器进位值,以此类推c2,c3值;两次压缩后 加法树的深度降低为2,最后通过加法器得到乘法运算的最终结果。

题目介绍:

设计一个高效的16bit有符号数定点乘法器乘数和被乘数均为16bit有符号随机数,输出为32bit有符号数。不限定乘法器的设计方案和形式,要求乘法器运算结果正确,且最大可能的降低资源消耗,提高性能。最大性能代价分满足设计要求 (资源代价得分,性能代价得分,将在第五部分详细介绍)。请根据要求规划该高效乘法器的结构并设计实现方案。

设计要求:

验收说明:

评分标准:

乘法器运算结果正确,通过随机数测试;

性能代价分不大于1000;

资源代价分不大于8000

准确统计出乘法器的资源代价分和性能代价分;

满足以上条件者方可进行有效评分;

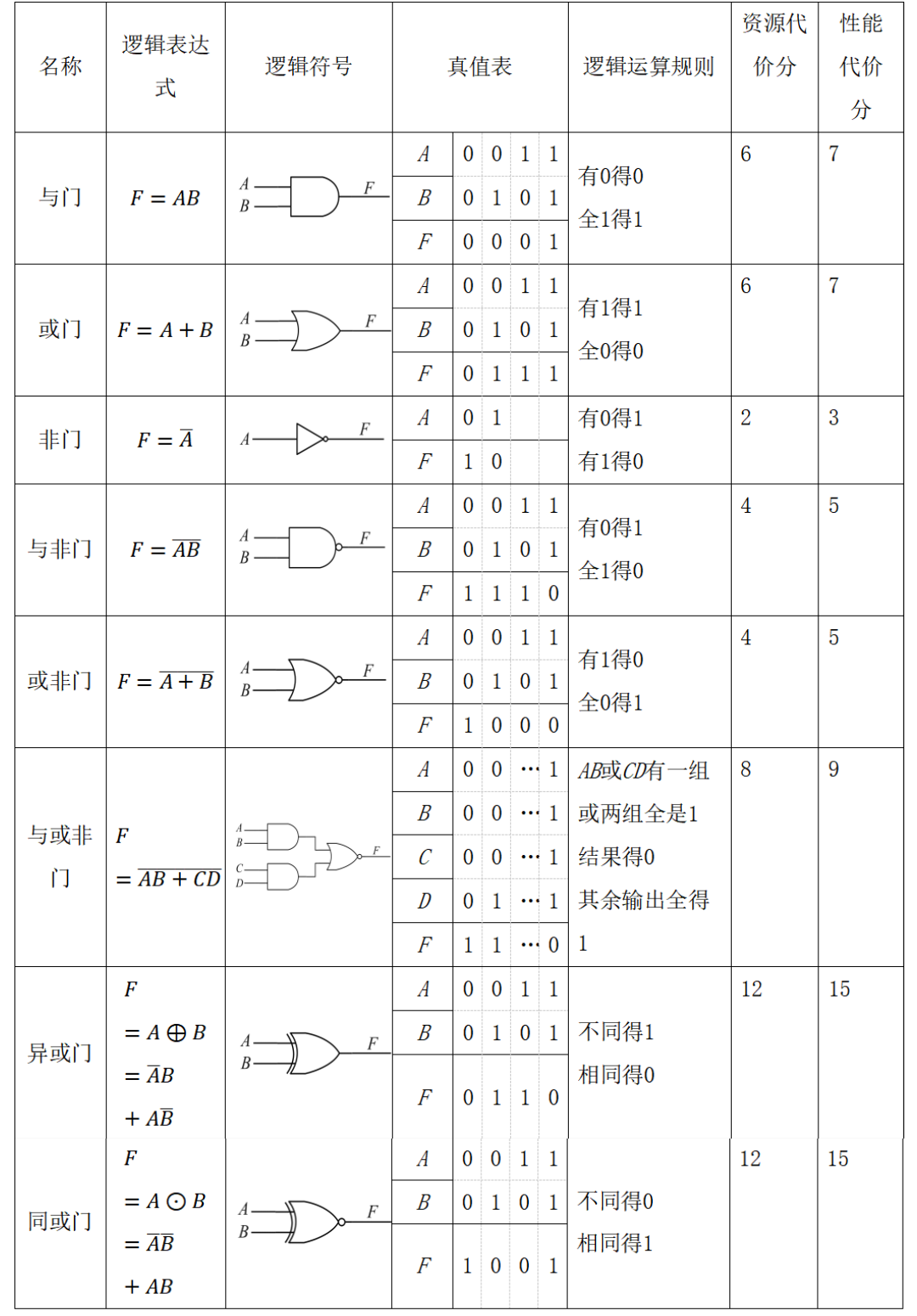

根据所有参考人员完成该乘法器消耗的资源代价打分。资源代价分为完成该乘法器设计使用附录1中逻辑门电路数量和其对应的资源代价分之积。如完成该乘法器使用了5个与门(与门的资源代价分为6),10个非门(非门资源代价分为2),则资源代价分为30+20分。资源代价分采用相对绝对模式,分数越低,得分越高:

≤5000 :得分50分,

≤6000 : 得分30分,

≤7000 : 得分10分。

根据所有参考人员完成该乘法器的性能代价打分。性能代价分考察对象为该乘法器设计的最长延时路径。统计最长延时路径使用附录1中逻辑门电路数量和其对应的性能代价分之积。如最长路径上使用了5个与门(与门的性能代价分为7),10个非门(非门性能代价分3),则设计者的性能代价分为35+30分。性能代价分采用绝对打分模式,分数越低,则排名越靠前:

≤500 : 得分35分,

≤600 : 得分20分,

≤800 : 得分10分。

根据所有参考人员的设计文档质量打分。文档要求:算法方案原理分析完备正确,设计文档描述详细,逻辑缜密;实现流程图,子模块的链接清晰关系,并能和交付代码完全对应;实现代码注释详细,通俗易懂;文档质量分采用绝对打分模式

文档交付完完备,工作原理分析正确,描述清晰易懂: 得分15分,

附录1:

该乘法器可能用到的八种常用逻辑门(逻辑表达式、逻辑符号、真值表、逻辑运算规则)

赛题十一:ASIC芯片物理设计中的Path Group规划算法

赛题十一、赛题十二测试集下载:https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=2435b87d92f74a748bc33211605eb59a

描述及要求:

Netlist是ASIC芯片物理设计的输入件,其中定义了数以百万计的standard cell之间的连接情况。物理设计EDA工具会基于netlist完成standard cell的placement、routing以及PPA优化等任务。其中,定义path group是一种常见的PPA优化方法,它通过识别设计中的关键时序路径,定义关键时序路径在时序优化过程中的权重分级,引导工具的优化。具体来说,为了定义path group,需要给定一条或一组时序路径的起点寄存器和终点寄存器(多个寄存器可借助通配符*表达)以及该path group的优化权重。通常path group需要根据placement阶段后的时序情况来定义,将时序较差的若干路径设置为高权重的path group,具体操作中需要多次迭代与试错,效率较低。因此本课题希望能够寻找一种方法,基于原始的netlist文件,通过图论领域中的路径搜索、partition、连接复杂度分析等算法,在物理设计前发现设计中的潜在时序路径瓶颈,并形成path group约束传递到EDA工具中,以期引导工具达成更好的QoR结果。

要求1:在给定的测试集上完成netlist网表到图数据(由节点和边以及相关属性组成)的转换。

测试数据集

要求2:在由上一步建模得到的图上,搜索寄存器到寄存器的时序路径、用适当的方式表征路径时序风险、按照时序风险对时序路径进行排序并完成时序关键路径的识别(以上可以只精确到路径的起点和终点)。可利用路径经过的节点数、每个节点的入度、出度或者其他合理方式表征路径的时序情况。

要求3:能够基于图上的时序情况预估结果,形成EDA工具可读的path group约束,并根据时序的瓶颈程度进行分级。即最终需要给出各path group的起点、终点和优化权重/优先级。

评审得分点:

输出要求:

赛题十二:ASIC芯片物理设计中的high fanout寄存器识别算法

描述及要求:

Netlist是ASIC芯片物理设计的输入件,其中定义了数以百万计的standard cell之间的连接情况,物理设计EDA工具会基于netlist完成standard cell的placement、routing等任务。其中,寄存器输出端的信号通过组合逻辑网络会传播到其他寄存器的输入端,通常从某一个寄存器出发,信号会传播到很多个寄存器(这些寄存器的数量常称为fanout数量)。当某寄存器的fanout数量很多时,它有可能会成为整个设计的时序与功耗瓶颈。因此,能够高效的在设计早期发现high fanout寄存器对设计优化十分有帮助。

要求1:在给定的测试集上,完成netlist网表到图数据(由节点和边以及相关属性组成)的转换。

测试数据集

要求2:在转换得到的图上,完成寄存器fanout搜索算法,搜索某个寄存器通过组合逻辑网络能传播到多少寄存器的输入端。

要求3:能够基于搜索算法的结果统计所有寄存器的fanout数量,并输出报告。

评审得分点:

输出要求:

第六届中国研究生创芯大赛承办单位介绍

第六届中国研究生创“芯”大赛承办单位华中科技大学坐落于湖北省武汉市,是国家教育部直属重点综合性大学、国家“211工程”重点建设和“985工程”建设高校之一,也是首批“双一流”建设高校。学校校园占地7000余亩,园内树木葱茏,碧草如茵,绿化覆盖率72%,被誉为“森林式大学”。学校师资力量雄厚,并遵循“应用领先、基础突破、协调发展”的科技发展方略,构建起了覆盖基础研究层、高新技术研究层、技术开发层三个层次的科技创新体系。

华中科技大学集成电路学院以服务国家重大战略和区域经济发展为目标,承建集成电路科学与工程和电子科学与技术两个一级学科,电子科学与技术、集成电路设计与集成系统、微电子科学与工程三个国家一流本科专业,先后获批国家集成电路人才培养基地、国家示范性微电子学院、国家集成电路产教融合创新平台。学院按照“国际视野、拔尖示范、协同育人、自主创芯、服务地方"的思路 ,通过人才培养、科学研究、学科建设“三位一体”,充分发挥产教融合优势,支撑和引领华中地区集成电路产业高速发展。

武汉东湖新技术开发区简称东湖高新区,又称中国光谷、简称光谷,于1988年创建成立,是中国首批国家级高新区、第二个国家自主创新示范区、中国(湖北)自由贸易试验区武汉片区,并获批国家光电子信息产业基地、国家生物产业基地、央企集中建设人才基地、国家首批双创示范基地等。 经过30多年的发展,东湖高新区综合实力和品牌影响力大幅提升,知识创造和技术创新能力提升至全国169个国家级高新区第一,成为全国10家重点建设的“世界一流高科技园区”之一。