奖项设置:

一等奖2队,奖金10,000元/队;

二等奖4队,奖金5,000元/队。

赛题咨询邮箱:

赛题一

基于多串动力锂电池SOX(SOC、SOH、SOP)动态高精度估算的算法

发展新能源是我国应对气候变化、推动绿色发展的战略举措。国家关于“四个革命、一个合作”能源安全新战略,实现碳达峰、碳中和战略目标,支撑构建新型电力系统,加快推动新型储能高质量规模化发展要求,催生了新能源大发展的机会。

锂离子电池作为储能单元在新能源领域得到广泛应用。然而,锂离子电池系统具备容量大、串并联节数多,系统复杂的特点,加之安全性、耐久性、动力性等性能要求高、实现难度大,因此成为影响新能源推广普及的瓶颈。

电池管理系统(BMS)的重要任务是保证电池系统的设计性能,主要可分解成安全性、耐久性、动力性三大方面。BMS由各类传感器、执行器、控制器以及信号线等组成,为满足相关的标准或规范,BMS功能需求包括电池电压、电流、温度等模拟量测量、采样频率同步性、SOC、SOH、SOP估算等等。

本命题重点考察BMS的设计性能优化方案,旨在以较低的资源开销,实现或提高相关SOX的精度,保证电池系统的安全性和使用寿命,同时提高功率的识别度,优化功率的输入输出平滑性,提高系统工作的稳定性。

基础分:

|

序号 |

类型 |

分值 |

要求描述 |

备注 |

|

1 |

MATLAB建模、仿真 |

65 |

实现MATLAB建模、仿真 |

使用60-100串,得65满分 |

|

3 |

SOC精度(X) |

5 |

实现3.5%≤X<4% |

|

|

4 |

SOH精度(Y) |

5 |

实现6%≤Y<8% |

|

|

5 |

SOP精度(Z) |

5 |

实现3.5%≤Z<4% |

|

|

6 |

ADC采样精度 |

10 |

采样精度≤14bit |

|

|

7 |

采样频率 |

10 |

采样频率≤4Hz(电池全部测量完一次) |

|

|

基础总分 |

100 |

*以使用60-100串建模为例 |

||

附加分:

|

序号 |

类型 |

分值 |

要求描述 |

备注 |

|

1 |

建模分 |

15 |

自行建模锂电池模型 |

|

|

2 |

SOC精度(X)优化 |

10 |

实现3%≤X<3.5% |

|

|

3 |

20 |

实现X<3% |

||

|

4 |

SOH精度(Y)优化 |

10 |

实现5%≤Y<6% |

|

|

5 |

20 |

实现Y<5% |

||

|

6 |

SOP精度(Z)优化 |

10 |

实现3%≤Z<3.5% |

|

|

7 |

20 |

实现Z<3% |

||

|

8 |

ADC采样精度优化 |

10 |

采样精度<14bit |

采样精度越低,可获得越多额外加分,单项满分10分 |

|

9 |

采样频率优化 |

10 |

采样频率<4Hz |

采样频率越低,可获得越多额外加分,单项满分10分 |

|

10 |

创新分 |

5 |

算法创新度 |

根据算法创新度加分,单项满分5分 |

|

最高附加分合计 |

100 |

|||

[1]陈翼星.锂电池SOC估计算法研究[D].西南交通大学,2018

[2]刘熹,李琳,刘海龙.动力型锂电池SOC与SOH协同估计[J].太赫兹科学与电子信息学报,2020,18(04):750-755

赛题二

高响应性信号处理SoC架构设计优化

高性能数模混合控制芯片是工业4.0落地的一个重要基础,大量的工业闭环控制,比如机械臂、滑轨、AGV等应用,都需要芯片来实现高速精准控制。

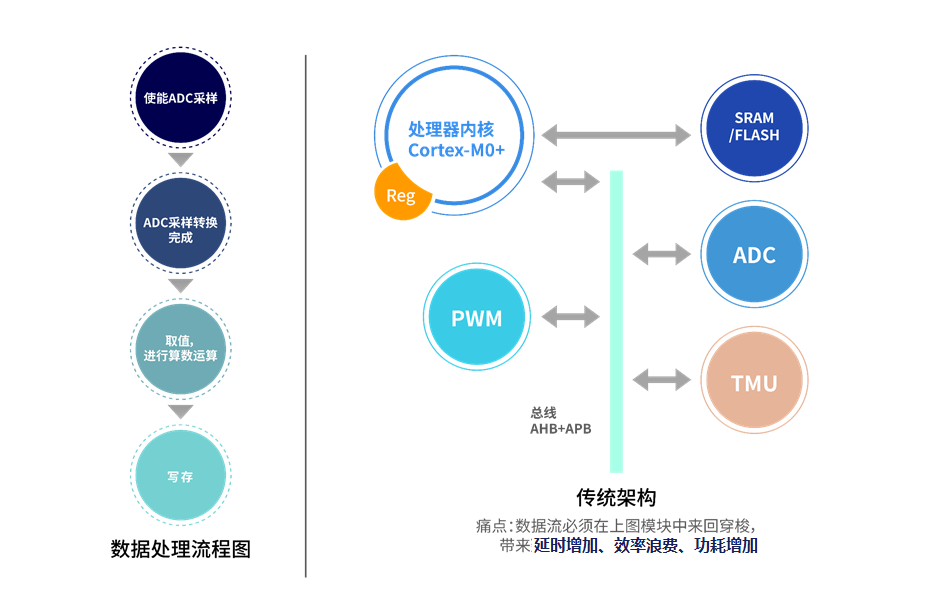

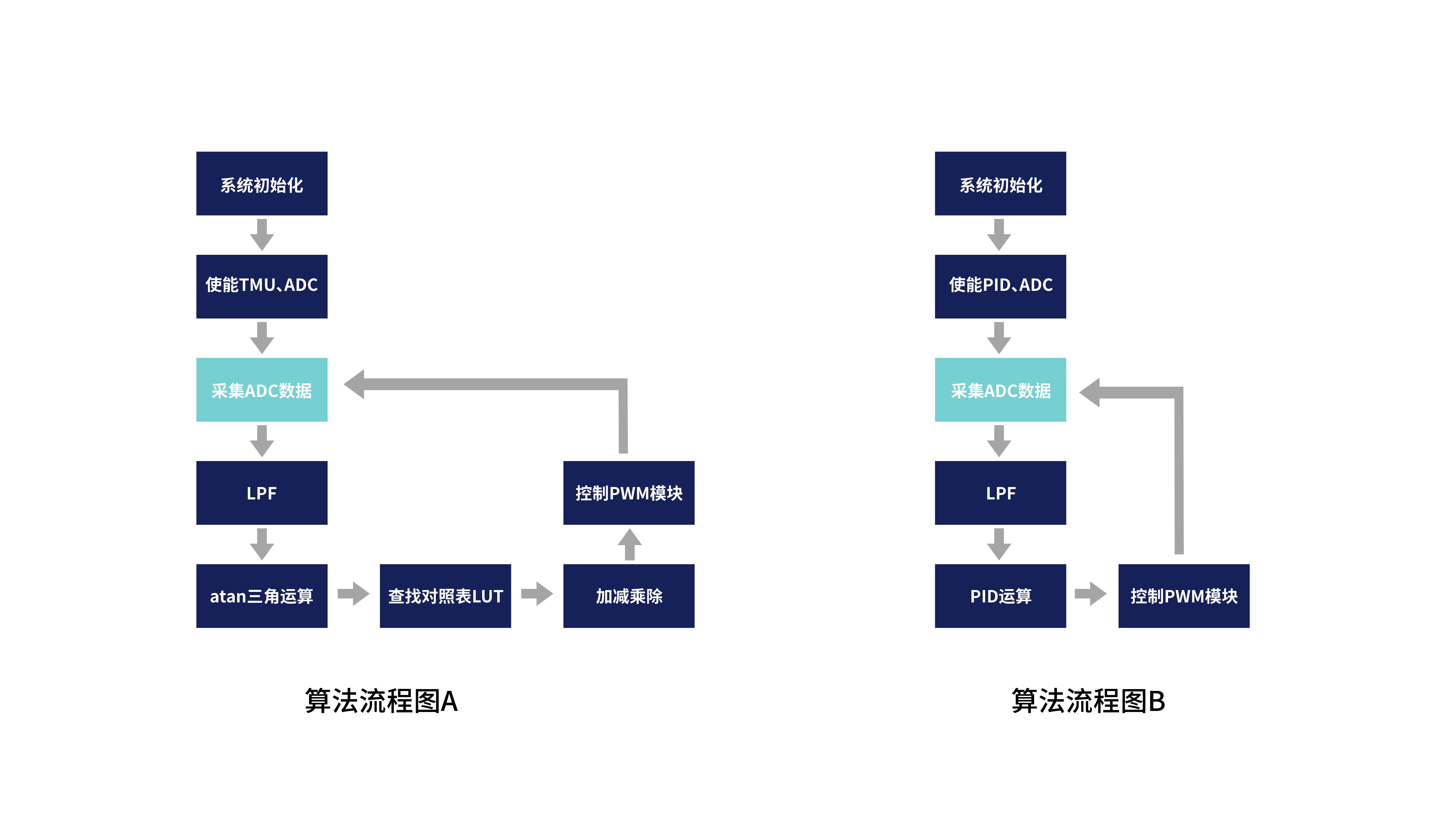

高性能数模混合控制芯片的其中一个难点,是如何对采集到的模拟信号进行高效预处理。这里涉及到高响应性信号处理SoC架构的创新。下图描述了工业级常见的处理架构,以及存在的痛点。

这个竞赛题目,希望同学们可以发挥创造力,解决这个痛点。

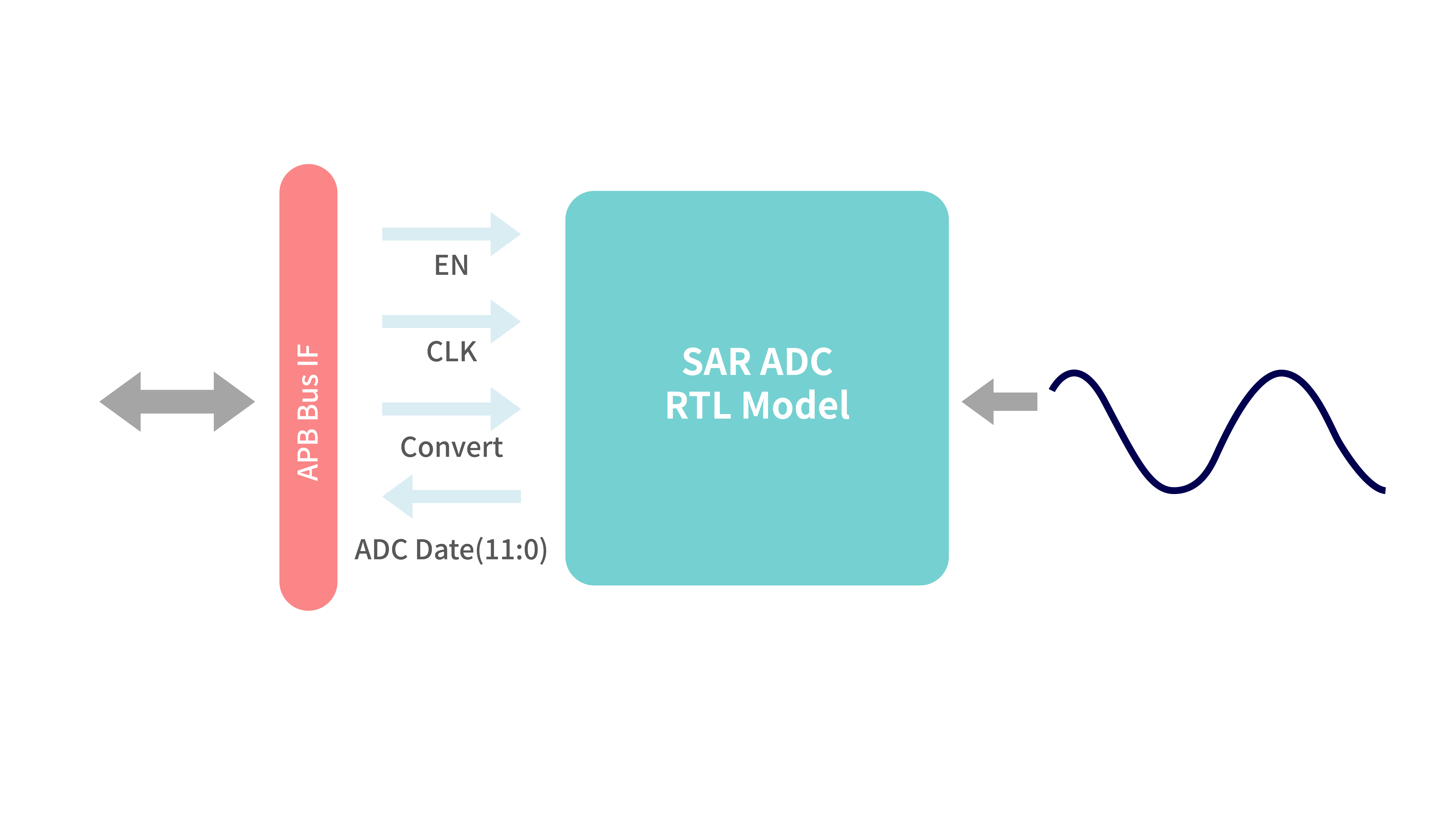

ADC模块包括(参考下图):

(1)ADC功能建模(模拟输入(real变量)→数字输出(寄存器变量)

(2)ADC时序建模(启动数据转换→转换完成数据写入寄存器→输出标记或中断)

(3)根据所选用的ADC架构正确描述ADC的数据转换时间

(4)ADC模块属于APB总线上的IP,需要包含APB控制接口

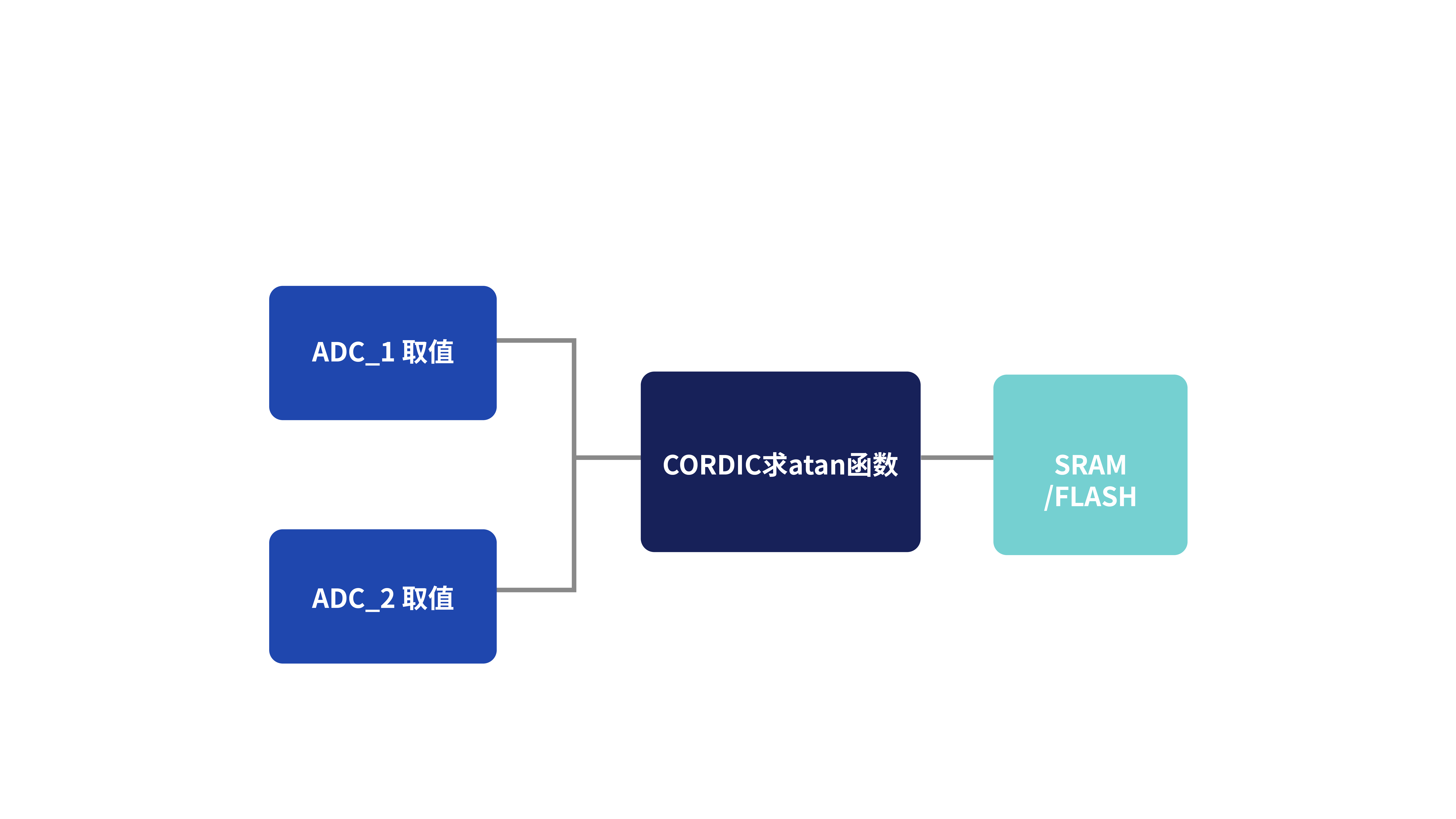

4.拼接后的系统,要求能实现上图“数据处理流程图”的功能,抽象的计算通路如下:

为了鼓励同学们探索更大的优化空间,可参考如下典型算法流程图A/B对架构进行优化。鼓励同学们实现完整的PID算法。

5.针对延时、处理器效率、面积、可迁移性4点做优化创新

(1)提出假设

(2)找出瓶颈

(3)提出思路

(4)验证思路

|

序号 |

类型 |

分值 |

要求描述 |

备注 |

|

1 |

基础得分 |

60 |

完成基于传统架构的信号处理SoC芯片,实现算法A与算法B的主要功能,在给定50MHz时钟频率下测量实现算法A与算法B所消耗的总时间,给出详细的设计报告与性能测试方案。 |

(1) 在实现算法A时,要求进行atan运算求出θ值在-90到90度以内精度做到误差不超过3%。 |

|

2 |

延迟测评附加分 |

16 |

相比于原始版本的架构设计,在50Mhz频率下完成A/B算法一次完整运算所用时间减少的比重,给出详细的对比报告和分析报告,指出不同的优化技术对延迟优化的贡献。 |

优化方案经评审方判断有效无虚报后进行排名,优化后所用时间越少排名越靠前。 |

|

3 |

效率测评附加分 |

12 |

减少运算过程中CPU介入的机器周期 |

优化后CPU介入时间越少排名越靠前。 |

|

4 |

面积测评附加分 |

8 |

输出FPGA综合报告 |

Logic Element数量越少排名越靠前。 |

|

5 |

可迁移性测评附加分 |

4 |

兼容不同内核平台 |

数量越多,排名越靠前(可并列)。 |

|

最高总分 |

100 |

|

||

附:

【1】CORDIC. CORDIC(Coordinate Rotation Digital Computer)算法即坐标旋转数字计算方法,是J.D.Volder1于1959年首次提出,主要用于三角函数、双曲线、指数、对数的计算。. 该算法通过基本的加和移位运算代替乘法运算,使得矢量的旋转和定向的计算不再需要三角函数、乘法、开方、反三角、指数等函数。

【2】LPF算法,可以参考公式Y(k) = Y(k-1) + LPF_Coefficient*(X(k) – Y(k-1))

参考文档:

https://github.com/srohit0/CORDIC

https://robotics.sjtu.edu.cn/upload/course/1/files/Chapter51.pdf