泰瑞达企业命题专项奖设置:

泰瑞达企业命题专项奖专门用于奖励选择泰瑞达企业命题的赛队,泰瑞达企业命题专项奖是初赛奖,由企业专家评出。入围决赛的参赛队伍继续参加大赛决赛奖项评比,与初赛奖项互不冲突。

泰瑞达企业命题专项奖设:

一等奖1队,每队奖金1万元

二等奖3队,每队奖金0.5万元

赛题文档下载链接

https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=3c5cf8b2e63d46d3827ee0d05c22a9da

芯片自动化测试设备(ATE)是半导体高端设备中的一类,其技术进步本身基于芯片设计与制造技术的进步,同时又存在如何使用已有芯片(有限性能)测试未来芯片(更高性能)的挑战。越发复杂的测试需求对测试设备和系统搭建提出了更高的挑战,提供超过高性能被测对象(DUT)更高性能的信号源是挑战之一。在固有物理性能极限限制下,新兴的的AI技术为我们提高信号源信号质量打开了全新的思路。我们在探索将现有硬件系统搭配AI技术得以实现性能突破的可能。

1.报名参赛的前三十只队伍凭预研方案(PPT),将获得泰瑞达提供的一套参考信号发生与采集硬件电路。预研方案中包括但不限于:

该硬件电路仅作为参考,参赛队伍可以自行搭建或利用已有硬件电路实现功能。

2.参赛者可自由选择在仿真环境中完成优化设计或利用实际系统硬件平台完成优化设计,可自由选择采用MCU/ARM/DSP/FPGA/PC等任何系统实现。例如:利用提供的参考硬件电路中的D/A生成正弦信号,并利用A/D测量生成信号的主要指标(SNR,THD)。

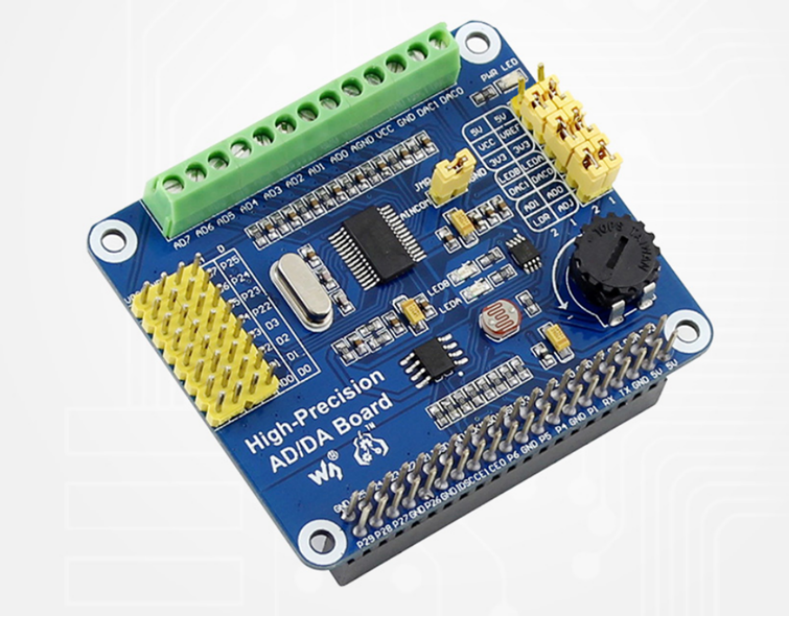

https://www.waveshare.net/shop/High-Precision-AD-DA-Board.htm

AD: ADS1256, 24-bit 8 Channel, data rate up to 30ksps (Teradyne ADC team developed the test solution for this device on FLEX platform:>)

DA: DAC8552, 16-bit 2 Channel, settling time 10us

在集成电路行业,随着芯片设计和制造技术的进步,程序规模日益增大,越来越多的项目采用高速迭代的敏捷开发模式,由此为开发及测试人员带来项目周期短,复杂度高的挑战。如果设计一个智能分析器,以自动化分析程序的逻辑及执行流程,并生成UML的时序图,以图形的方式直观表现出程序架构,就可以有效地提高代码分析的效率,缩短项目迭代周期。

1.根据分析工具支持的程序复杂度:

2.设计文档的完整性及可读性;

3.源代码的可读性;

4.使用自主研发的语法分析器加分

5.使用自主研发时序图生成器加分

6.可支持多语言环境加分;

7.如果参赛队伍为非首次参赛,请提供与以往方案相比的创新点与优化效果;

第六届中国研究生创芯大赛承办单位介绍

第六届中国研究生创“芯”大赛承办单位华中科技大学坐落于湖北省武汉市,是国家教育部直属重点综合性大学、国家“211工程”重点建设和“985工程”建设高校之一,也是首批“双一流”建设高校。学校校园占地7000余亩,园内树木葱茏,碧草如茵,绿化覆盖率72%,被誉为“森林式大学”。学校师资力量雄厚,并遵循“应用领先、基础突破、协调发展”的科技发展方略,构建起了覆盖基础研究层、高新技术研究层、技术开发层三个层次的科技创新体系。

华中科技大学集成电路学院以服务国家重大战略和区域经济发展为目标,承建集成电路科学与工程和电子科学与技术两个一级学科,电子科学与技术、集成电路设计与集成系统、微电子科学与工程三个国家一流本科专业,先后获批国家集成电路人才培养基地、国家示范性微电子学院、国家集成电路产教融合创新平台。学院按照“国际视野、拔尖示范、协同育人、自主创芯、服务地方"的思路 ,通过人才培养、科学研究、学科建设“三位一体”,充分发挥产教融合优势,支撑和引领华中地区集成电路产业高速发展。

武汉东湖新技术开发区简称东湖高新区,又称中国光谷、简称光谷,于1988年创建成立,是中国首批国家级高新区、第二个国家自主创新示范区、中国(湖北)自由贸易试验区武汉片区,并获批国家光电子信息产业基地、国家生物产业基地、央企集中建设人才基地、国家首批双创示范基地等。 经过30多年的发展,东湖高新区综合实力和品牌影响力大幅提升,知识创造和技术创新能力提升至全国169个国家级高新区第一,成为全国10家重点建设的“世界一流高科技园区”之一。