概伦电子赛题专项奖设置:

概伦电子企业命题专项奖专门用于奖励选择概伦电子企业命题的赛队,概伦电子企业命题专项奖是初赛奖,由企业专家评出。入围决赛的参赛队伍继续参加大赛决赛奖项评比,与初赛奖项互不冲突。

概伦电子专项奖设:

一等奖2队,每队奖金1万元

二等奖6队,每队奖金0.5万元

为帮助选择概伦电子企业命题的参赛队伍提升专业技能水平,取得理想成绩,概伦电子将通过邮箱申请方式提供全定制电路设计平台NanoDesigner与建模软件MeQLab的软件及账号,申请软件的条件及软件发放方式如下:

1、队伍需要报名概伦电子赛题

2、软件申请表邮件需要通过所在学校官方后缀的邮箱发送至shenjj@primarius-tech.com

3、完成以上两个条件的报名队伍,概伦电子将在每周三及周五发放软件及账号

3、因软件账号需要自行注册,请加入概伦电子企业命题交流群,以便获取更多概伦电子最新通知。

4、若有其它疑问请联系秘书处微信cpicic-ctri

软件申请表下载链接

https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=36feaca089d74d6ea0c2cea43a908e7f

Linux系统安装插件(腾讯微云下载)

https://share.weiyun.com/Vb1TGFAR

概伦电子赛题讲解及工具培训视频

【2023年中国研究生创“芯”大赛-概伦电子企业命题讲解】

https://www.bilibili.com/video/BV1yL411S7vu/?share_source=copy_web&vd_source=731983d24066c046753f8a80d7ad6bd5

请使用概伦电子提供的电路/版图设计工具 Nanodesigner , 以及spice 仿真工具Nanospice, 基于本题附录1提供的PDK(仅可使用该PDK所提供器件),设计一个高精度的RC振荡器。要求该振荡器输出时钟频率达到约16MHz,输出时钟占空比约为45%~55%,电源电压范围为 2.7V~3.6V。

任务1、给出所设计高精度RC 振荡器的电路图,并逐一解释所选用的器件及器件参数的设定;阐述该电路各组成模块的基本功能和工作原理;给出设计报告。(25分)

任务2、完成所设计RC振荡器的电路仿真工作。要求给出电路仿真的testbench, 以及Typical PVT (TT/3.3v/25C) 下的仿真结果,包括输出频率测量结果,占空比测量结果,工作电流测量结果。(25分)

任务3、完成固定Process 为TT时各电压、温度组合下的仿真工作。要求给出电路仿真的输出频率、占空比、工作电流,并统计输出频率在各corner下的频率偏移百分比。(50分)

5.各PVT corner (固定TT process,电压变化范围为【2.7V, 3.6V】,温度变化范围为【-40C,125C】)下,输出时钟频率变化范围尽可能小,评分标准可参照以下要求。(30分)

赛题一附件:Prims_lib-iPDK-demo.tar

下载链接

https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=ab17b0ac017c4cf2b4a7b0a26633b534

注:概伦电子建模软件MeQLab介绍

MeQLab是一款灵活的跨平台建模软件,适用于Windows和Linux等操作系统。MeQLab平台提供了器件模型提取的完整解决方案:从最初的器件测试、数据分析、模型提取、Corner提取、统计模型提取再到模型验证和报表输出均可实现在同一软件平台,可满足从基带、小信号建模到大信号验证一站式建模应用。MeqLab内置NanoSPICE仿真器,同时支持链接外部仿真器(如HSPICE、Spectre等),且支持多仿真器的并行仿真验证。其不仅支持业界标准的Compact模型包括最新的FinFet及化合物器件模型如ASM-HEMT,还支持子电路模型,Verilog-a模型, 以及基于子电路的BSIM模型衍生的高压模型的提取。基于器件类型,为用户提供了一系列射频建模应用模板,同时内嵌脚本编程环境,开放用户自定义应用模块如去嵌、模型自动提取等。

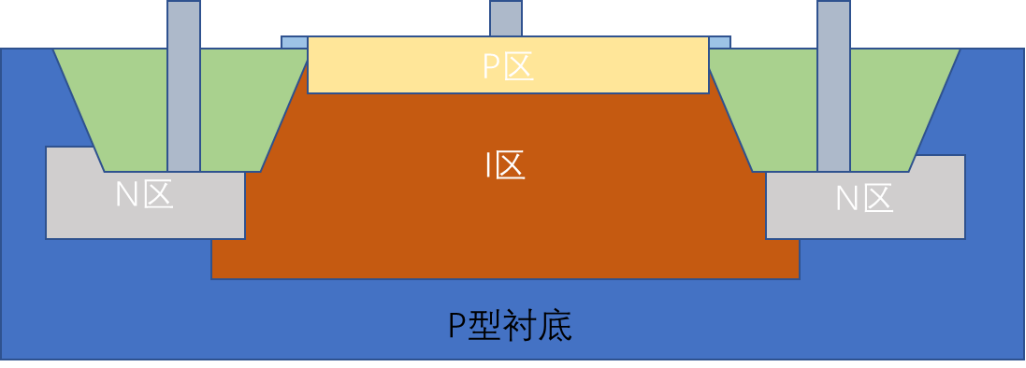

任务1、某专利中兼容BiCMOS工艺的PIN Diode剖面结构如图1所示,试给出该PIN Diode的制备工艺流程,并给出该工艺流程中每步光刻步骤对应的掩膜版图形;在图1中标注PIN Diode正向工作时的电流方向和电路流动路径,分析该路径上影响器件插入损耗的关键结构参数及影响机制。(20分)

图1. 某PIN diode结剖面图

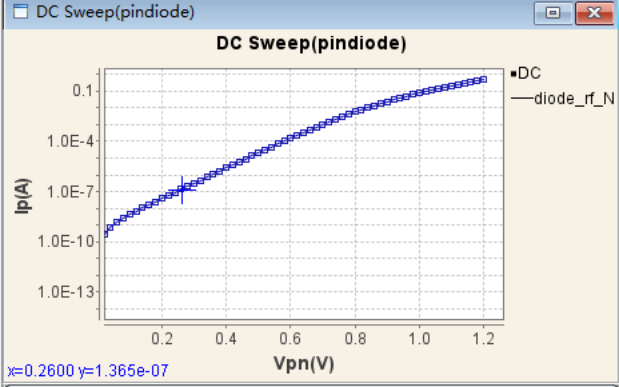

任务2、基于PIN Diode模型仿真所产生的正向IV特性曲线如图2所示,分析理想PIN Diode和理想PN Diode正向、反向电学特性的差别及产生原因。参考以上分析,试给出能够表征PIN Diode正向和反向特性的等效电路,并设计测试方法来表征PIN Diode的正向、反向电学特性(15分)。

图2. 硅基PIN Diode模型仿真所生成的正向IV曲线

任务3、利用所给教程,学习、了解MeQLab的使用方法,给出在MeQLab中进行Diode手动参数提取的主要流程 (15分)。

任务4、根据附件2提供的PIN Diode在不同温度、不同尺寸下的I-V测量数据、C-V测量数据和初始模型,完成如下建模提参任务。

任务5、给出本次建模报告和模型文件,并进行综合性小结。(10分)

赛题二、赛题三附件:Khailong_RefDataModel

下载链接

https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=844bf12052ed4dc784224353e6edf226

MeQLab是一款灵活的跨平台建模软件,适用于Windows和Linux等操作系统。MeQLab平台提供了器件模型提取的完整解决方案:从最初的器件测试、数据分析、模型提取、Corner提取、统计模型提取再到模型验证和报表输出均可实现在同一软件平台,可满足从基带、小信号建模到大信号验证一站式建模应用。MeqLab内置NanoSPICE仿真器,同时支持链接外部仿真器(如HSPICE、Spectre等),且支持多仿真器的并行仿真验证。其不仅支持业界标准的Compact模型包括最新的FinFet及化合物器件模型如ASM-HEMT,还支持子电路模型,Verilog-a模型, 以及基于子电路的BSIM模型衍生的高压模型的提取。基于器件类型,为用户提供了一系列射频建模应用模板,同时内嵌脚本编程环境,开放用户自定义应用模块如去嵌、模型自动提取等。

使用概伦电子的建模软件MeQLab完成下列题目

针对某一器件,完成器件结构和工艺流程解析、建模、参数提取及拟合精度分析。不限定器件类型、制备工艺,例如可以是MOSFET、BJT、diode等器件。

第六届中国研究生创芯大赛承办单位介绍

第六届中国研究生创“芯”大赛承办单位华中科技大学坐落于湖北省武汉市,是国家教育部直属重点综合性大学、国家“211工程”重点建设和“985工程”建设高校之一,也是首批“双一流”建设高校。学校校园占地7000余亩,园内树木葱茏,碧草如茵,绿化覆盖率72%,被誉为“森林式大学”。学校师资力量雄厚,并遵循“应用领先、基础突破、协调发展”的科技发展方略,构建起了覆盖基础研究层、高新技术研究层、技术开发层三个层次的科技创新体系。

华中科技大学集成电路学院以服务国家重大战略和区域经济发展为目标,承建集成电路科学与工程和电子科学与技术两个一级学科,电子科学与技术、集成电路设计与集成系统、微电子科学与工程三个国家一流本科专业,先后获批国家集成电路人才培养基地、国家示范性微电子学院、国家集成电路产教融合创新平台。学院按照“国际视野、拔尖示范、协同育人、自主创芯、服务地方"的思路 ,通过人才培养、科学研究、学科建设“三位一体”,充分发挥产教融合优势,支撑和引领华中地区集成电路产业高速发展。

武汉东湖新技术开发区简称东湖高新区,又称中国光谷、简称光谷,于1988年创建成立,是中国首批国家级高新区、第二个国家自主创新示范区、中国(湖北)自由贸易试验区武汉片区,并获批国家光电子信息产业基地、国家生物产业基地、央企集中建设人才基地、国家首批双创示范基地等。 经过30多年的发展,东湖高新区综合实力和品牌影响力大幅提升,知识创造和技术创新能力提升至全国169个国家级高新区第一,成为全国10家重点建设的“世界一流高科技园区”之一。