格科微企业命题专项奖

格科微企业命题专项奖专门用于奖励选择格科微企业命题的赛队,由企业专家评出。格科微企业命题专项奖是初赛奖,入围决赛的参赛队伍继续参加大赛决赛奖项评比,与初赛奖项互不冲突。

奖项设置

一等奖赛队2支,每队奖金1万元;

二等奖赛队6支,每队奖金5千元;

格科微-创芯大赛人才政策

格科微电子(上海)有限公司希望从创芯大赛获奖学生中挖掘人才,并在招聘中提供快速通道。参加创芯大赛的获奖学生,投递芯片类岗位:1. 获全国二等奖三等奖学生,可以免笔试;2. 获一等奖及以上学生,可直接进入综合面试;3. 格科专项奖等级等同全国奖对应等级待遇。

赛题文档下载链接

https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=ee69e49412e44ee597f01b6a49fdea89

格科微专家讲解赛题视频

【2023年中国研究生创“芯”大赛-格科微企业命题讲解】

https://www.bilibili.com/video/BV13m4y1z7fJ/?share_source=copy_web&vd_source=731983d24066c046753f8a80d7ad6bd5

课题背景:

在安防监控、物联网、自动驾驶等应用场景下,为实现多种信息和信号的采集,各类传感器得到广泛的使用。其中,CMOS图像传感器(CMOS Image Sensor,CIS)作为获取环境图像信息的核心元件被广泛使用。而在CIS系统中,模数转换器(Analog-to-Digital Converter,ADC)是对图像信号处理的重要电路模块,对系统性能起到了决定性作用。在ADC结构上,CIS通常要求在一行像素的读出时间内完成当前行所有像素的量化,为实现速度和功耗的折衷,目前广泛采用列并行的多通道ADC结构,这对ADC的面积有较为严格的限制。另一方面,传感器广泛应用在采用电池供电的移动设备中,部分应用还要求传感器长期处于工作状态(always-on),这对芯片功耗也提出了严格的要求。随着目前各类应用场景对获取图像动态范围更高的需求,CIS中ADC的精度要求也不断提高,而如何在面积和功耗有较为严格的限制下实现高精度ADC是目前的设计挑战。

课题内容及要求:

1. 设计一款支持1000个通道数据处理的多通道高精度ADC(阵列),完成电路及版图设计;

2. 所有通道的输入均为低频电压信号(在转换时间内可近似为直流信号),电压变化范围为1V,处于1V~2V之间;

3. ADC精度要求为14bit, 1000通道总功耗不大于100mW,转换时间不大于2.5μs;

4. 假定信号为Y方向输入,则ADC主体电路版图在X方向总长度≤3000μm(单通道≤3μm),Y方向长度不限,但越小越好;

5. 建议使用特征尺寸≤65nm的工艺设计,可采用电源电压为2.8V/1.8V/1.2V。

评审得分点:

1. 调研与课题分析(10分):针对课题要求进行充分调研,给出ADC结构选择的理由;

2. 电路设计及仿真分析(40分):ADC设计符合题目要求,给出完整的设计及仿真分析报告,仿真结果(后仿真)达到各项指标要求;

3. 版图设计(10分):满足题目要求,总面积尽量小;

4. 多通道性能表现(20分):针对通道之间的数据一致性及串扰进行仿真分析;

5. 设计的新颖性(10分):ADC结构选择及电路设计具有创新性;

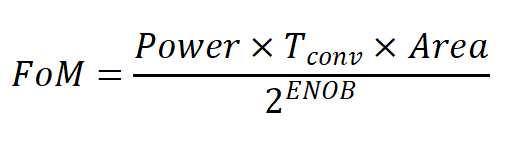

6. 指标的竞争力(10分):ADC综合指标具有竞争力,根据FoM进行评估。

课题目标:

1. 能够分析出课题主要设计要点,完成从前期调研到后期的后仿验证全部过程,完成设计报告,报告中包含所有课题内容;

2. 设计结果必须功能正确,最好能够与实验室固有研究课题相结合,使面积、功耗以及速度性能综合评分能够与调研结果可比;

3. 能够针对设计中遇到的问题,合作思考解决,设计中有一定的设计创新之处。

课题输出:

1. 设计报告,包括调研分析、原理图、版图、仿真结果等;

2. 设计中的难点解决与团队合作过程心得小结。

课题背景:

锁相环(PLL)是一种反馈控制电路,其工作特点是利用外部输入的参考信号控制环路内部振荡信号的频率和相位,在通信系统、数据存储、数据传输等应用中都是必不可少的电路模块。根据其振荡器的类型,锁相环可以分为环形振荡器PLL和LC振荡器PLL。由于两种锁相环的结构和性能差异,环振PLL常被用于较低频率的信号处理和传输,而LC PLL则常被用于较高频率的射频通信中,经验上认为环振PLL在较高频率时其噪声性能会越来越差。在图像传感器芯片应用中,考虑到工作频率、设计工艺、功耗和面积等因素,通常都是选择环振PLL。然而随着高像素产品不断升级,对芯片中PLL的工作频率和抖动要求都是越来越高,因此,设计高性能的片上高速环振锁相环成为产品应用升级中必须要解决的难题。

课题内容及要求:

1. 完成一个完整的环振PLL电路原理图和版图设计,要求PLL输出频率覆盖范围包含2.5GHz~5GHz(TT工艺下后仿真结果);

2. 建议使用特征尺寸≤65nm的工艺设计,可以是纯模拟或者数模混合电路,电路架构不限,限制输入参考频率≤24Mhz;

3. 给出PLL工作在4GHz时控制电压的锁定过程曲线以及输出信号的波形(后仿真结果);

4. 给出PLL工作在4GHz时的抖动或者相位噪声分析和仿真结果,提出并应用可行的相位噪声(抖动)优化方案;

5. 给出PLL电源叠加1MHz 40mV Vp-p正弦波噪声下的输出信号眼图,分析和仿真电源噪声对PLL抖动的影响,提出并应用可行的电源噪声抑制方案。

评审得分点:

1. 同等设计平台及相近的环路参数下,版图面积越小越好,功耗越小越好(限制PLL工作在4GHz时总功耗不能高于25mW);

2. 环路锁定时间25us以内,输出波形为稳定的方波信号;

3. 关键频偏处的输出相噪越小越好,或者输出信号的抖动越小越好,对电源地的噪声抑制越大越好(限制不加电源噪声时输出RMS Jitter不能高于15ps@4GHz,相位噪声以此抖动标准折算);

4. 设计中出现有效的突出创新点可加分,若设计工艺条件有限制,可适当降低PLL工作频率要求,但相应的得分会做对应的降低。

课题目标:

1. 能够分析出课题主要设计要点,完成从前期调研到后期的后仿验证全部过程,完成设计报告,报告中包含所有课题内容;

2. 设计结果必须功能正确,可以与实验室固有研究课题相结合,使面积、功耗以及噪声性能综合评分能够与调研结果可比;

3. 能够针对设计中遇到的问题,合作思考解决,设计中有一定的设计创新之处;

4. 不局限于典型的基于电荷泵的Ⅱ型PLL架构,可以自由发挥,符合课题内容及要求即可。

课题输出:

1. PLL电路设计报告,包括调研和建模分析过程、原理图、版图截图、功能和功耗仿真结果等,如果有数字模块,需要附上数字代码(60%:建模分析10%,原理图15%,版图20%,功能正确频率达到要求15%)

2. 相位噪声或抖动仿真和分析结果,电源噪声的影响仿真和分析结果,以及对应的优化方案;(30%)

3. 设计中的难点解决与团队合作过程心得小结(10%)

课题背景:

温度传感器(temperature sensor)是一种能感应温度,把温度转换成数字输出信号的传感器。随着芯片集成度越来越高,片上系统和应用环境越来越复杂,芯片的工作温度不再单一和可预知。为了确保芯片一直工作在最佳状态,必须实时监测芯片的工作温度,对关键参数进行实时调整。所以,在芯片上集成温度传感器成为一个重要的发展趋势。由于受到实际制造和芯片工作电压的影响,芯片和芯片之间存在差异,也就是说对于同一温度,温度传感器转换成的数字码不一致,这会导致关键参数调整存在偏差,芯片性能变差,所以如何修正温度传感器芯片和芯片之间的偏差也成为一个重要的研究课题。

课题内容及要求:

1. 完成一个完整的温度传感器原理图和版图设计,要求:

(1)温度测试范围-40~120℃;

(2)最终输出为与温度对应的数字码;

(3)蒙特卡洛(Monte carlo)仿真3σ≤0.5℃;

(4)总功耗≤1mW;

2. 建议使用特征尺寸≤65nm的工艺设计,温度传感器的架构不限,可以是纯模拟或者数模混合电路;

3. 设计过程中需要包含调研、仿真建模分析、理论计算分析、电路原理图和版图绘制、后仿真分析等,并最终体现在设计报告中。

评审得分点:

1. 完成电路设计,typical仿真温度转换精度达到0.5℃;(20分)

2. 完成版图设计,typical仿真温度转换精度达到0.5℃;(20分)

3. 提出校准方案,完成校准模块设计;(20分)

4. 蒙特卡洛(Monte carlo)仿真3σ≤0.5℃(20分)

5. 其他(20分)

(1)设计中出现有效的突出创新点

(2)满足设计的条件情况下,面积和功耗同比占优的

(3)满足Monte carlo仿真要求,校准电路自动化程度同比占优的

课题目标:

1. 能够分析出课题主要设计要点,完成从前期调研到后期的后仿验证全部过程,完成设计报告,报告中包含所有课题内容;

2. 设计结果必须功能正确,最好能够与实验室固有研究课题相结合,使面积、功耗以及精度等综合评分能够与调研结果可比;

3. 能够针对设计中遇到的问题,合作思考解决,设计中有一定的设计创新之处;

课题输出:

1. 设计报告,包括建模分析过程、原理图、版图截图、仿真结果等,如果有数字模块,需要附上数字代码

2. 给出电路的蒙特卡洛(Monte carlo)仿真结果,如有校准电路,给出校准前后的蒙特卡洛(Monte carlo)仿真对比结果

3. 设计中的难点解决与团队合作过程心得小结

课题背景:

消费电子芯片中,一些模块常需要被高于电源电压的高压驱动。综合考量效率、噪声、成本等因素,相比于传统的DC-DC转换电路,电荷泵(charge pump)作为传统的升降压电源转换电路,有很大的优势。因此,电荷泵在各种消费类电子芯片中,有着广泛的应用。一般地,电荷泵作为芯片内部模块电源,当负载跳变的时传统的稳压电荷泵的输出电压会有较大的抖动,且恢复时间跟工作的时钟频率有关,提高时钟频率会减小恢复时间,但是势必会增加系统的功耗;另一方面,与DC-DC开关电源类似,开关电源的噪声会降低具体的负载产生电路的SNR等性能,同样地,提高时钟频率会减小纹波,但是会增加功耗。传统的解决方法是采用片外电容,能较好的满足负载跳变时快速恢复和低纹波的需求。但考虑到系统的应用成本,无片外电容、电感是更理想的方案,因此,快速稳定和低纹波设计成为急需解决的难题。

课题内容及要求:

1. 完成无片外电感电容稳压电路的原理图和版图设计,片内可用电容<100pF;

2. 电源电压2.8V,输出电压可编程3V~4V,档间距0.1V;外部可供时钟频率25MHz。

3. 稳定工作时静态负载电流100uA,负载电容5pF。功耗<2.8mW,面积<100,000um2。

4. A:输出电压纹波<1mV;B:负载电容受干扰有-1V跳变时,输出电压稳定在跳变量0.1%内时间<10ns。

5. 工艺节点建议采用0.18um~40nm。

评审得分点:

1. 完成电路及版图设计,输出完整设计报告;(60分)

2. 功耗<2.8mW;(10分)

3. 版图面积<100,000um2 ;(10分)

4. 输出电压纹波<1mV;(10分)

5. 负载电容受干扰有-1V跳变时,输出电压稳定在跳变量0.1%内时间<10ns。(10分)

以上仿真指标以TT工艺角后仿真结果为准

课题目标:

1. 检索文献,对比实现快速稳定、低纹波稳压电路架构的优劣;(建议采用pump+LDO架构,LDO可采用FVF)

2. 理论推导出各指标;

3. 搭建电路,仿真电路各项指标,并与计算值对比。

4. 绘制完整版图,进行后仿真,并与前仿指标进行对比;

课题输出:

完整的设计报告,包括电路图截图、版图截图、详细理论分析、计算结果、仿真截图、计算值仿真值对比表。

课题背景:

消费电子设备,全面屏的普及以及终端客户对娱乐和游戏场景的越来越多的应用,使得芯片和设备的功耗越来越成为了制约消费电子使用的瓶颈。运算放大器电路是高精度模拟和混合模块设计中最重要的组件之一,其广泛用于实现积分器,微分器,信号缓冲,采样保持电路,模拟信号处理等电路中。而运放的关键参数包括,共模抑制比,输出摆幅,增益,摆率,输入共模范围,电源抑制比,功耗,噪声谱密度,输入输出阻抗等,根据具体应用和设计,考虑到集成电路中实现的运放的一些非理想特性,设计者们会做一定的权衡设计tradeoff。因此,为了追求实现极低功耗,长时间续航的同时,实现宽范围动态响应成为了新的设计挑战。nA级低失调轨到轨输入输出的运放设计成为急需解决的难题。

课题内容及要求:

1. 基于CMOS工艺,完成nA级低失调Rail-to-Rail单位增益运放电路的电路设计和版图设计;包含所有工艺角(TT,FF,SS,SF,FS),温度-40~85℃及电源电压6.4-6.6V 仿真结果;

2. 输入/输出电压范围0.1V~6.3V;增益>80dB, 相位裕度>60度, 静态功耗<100nA。

3. A:低失调offset<1mV (3sigma);B:输入幅度0.2-6.2V跳变时,输出电容上的电压稳定在0.1%内时间<5us。

4. 以上2和3,运放的输出到地的负载模型= 输出电阻R串联输出电容C连接到地;其中R=10K,C=50pF。

评审得分点:

1. 完成课题内容及要求1得20分;

2. 完成课题内容及要求1,2得50分;

3. 完成课题内容及要求1,2,3A或者1,2,3B得分60;

4. 完成课题内容及要求1,2,3A,3B得分70;

5. 同时完成2和3指标前提下,功耗最低+5分,面积最优+5分;

6. 架构创新+10分,电路创新+10分,总分100分。

7. 未完成版图,总分-10分;指标3A仅通过增加输入对管面积来实现的,总分-10分。

课题目标:

1.检索文献,对比实现nA级低失调Rail-to-Rail单位增益运放电路可行方案架构;(可选但不限于classAB架构)

2.理论分析出达成课题指标的关键因素;

3.搭建电路,仿真迭代电路各项指标,并与分析计算值对比;

4.绘制完整版图,进行后仿真,并与前仿指标进行对比。

课题输出:

1.完整的设计报告,包括电路图截图、版图截图、详细理论分析、计算结果、仿真截图、计算值仿真值对比表。

2.各工艺角下的管子工作状态(包含VGS/VDS/VTH/饱和/线性/亚阈值区等信息)的文档。

赛题六视频数据下载:

https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=76fdf8d2bacd43a58e5db2c73cc9621c

赛题六坐标计算dll下载:

https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=7661fbc976ea4fd9abd7d11758fc76d7

课题背景:

随着智能手机等便携设备的飞速发展,对屏幕触控交互的需求日益增加。在触控屏的实际使用中,存在大量来源于外界环境的干扰场景。这些外界干扰的剧烈程度甚至超过了触控本身,给使用者的体验造成影响。因此课题需要排除干扰,找出触控手指,提升用户体验,增加产品竞争力。

本课题已将“触控、屏幕与干扰”等实际场景,抽象为低分辨率纯视频数据(约为36*18像素)。需要请参加课题的学生,从算法角度出发,分辨出视频中出现的指定物体或干扰,排除干扰,恢复数据。

课题内容及要求:

1. (基本软件任务)完成一个适用于“行列噪声及重压形变”,即直线状动态干扰与区域状静态干扰的辨识修复算法设计,要求可以辨识出手指及干扰类型,并对干扰进行修复。算法类型不限,如基于传统CV或基于AI;

2. (进阶软件任务)完成一个适用于“共模干扰(5~10V的Vpp正弦波,1~200kHz)”,即区域状动态干扰的辨识修复算法设计,要求可以辨识出手指及干扰类型,并对干扰进行修复。算法类型不限,如基于传统CV或基于AI;

3. (基本硬件任务)在完成基本软件任务或进阶软件任务的条件下,将设计出的软件模型用数字集成电路HDL实现,完成编写、前仿、综合,评估时序与面积。

4. (附加硬件任务)在完成基本硬件任务的条件下,选手可以自行选用合适的平台,做成Demo展示效果。

说明:

1. 算法输入为课题中提供的视频组(两组对照,分为普通无干扰场景与各类干扰场景),输出为经算法处理后的视频和辨识类型结果;

2. 算法不能调用算法过程不明确的模块或函数;

3. 软件算法实现的编程语言,使用C、C++、Matlab或Python;

4. 硬件算法实现的编程语言,推荐使用Verilog或VHDL,其他HDL语言亦可;

5. 对时序及面积的评估,可以使用0.18um工艺仿真或quartus/vivado等FPGA评估逻辑单元;

评审得分点:

1. (基本软件任务)按客观辨识成功率及主观修复完整度两个指标综合考量;

2. (进阶软件任务)按客观辨识成功率及主观修复完整度两个指标综合考量;

3. (基本硬件任务)按任务完成度、综合时序和面积的指标综合考量;

4. (附加硬件任务)按任务完成度、展示效果综合考量;

说明:

1. 客观辨识成功率高指的是:辨识各类干扰类型的准确率高(准确率占比40%)、无干扰场景下误识为干扰的概率低(误识率占比20%)、干扰场景下识别为无干扰的概率低(漏识率占比40%);

2. 主观修复完整度高指的是:将受到干扰的数据修复为无干扰数据后,借助课题中提供的检测方案计算出触控坐标,评估坐标的可靠性(占比60%)和稳定性(占比20%),此外还需参考实时性(占比20%);

3. 可靠性指的是:坐标点单一,没有额外多的坐标点(误报率)和缺失的坐标点(漏报率);

4. 稳定性指的是:坐标点尽量保持稳定,抖动越少得分越高;

5. 实时性指的是:需要延迟得出结果的算法,延迟帧数越少得分越高;

6. 最终得分权重占比:基本软件任务30% + 进阶软件任务30% + 基本硬件任务40% + 附加硬件任务额外20%;

课题目标:

1. 完成从算法调研到算法实现及验证的全部过程,完成算法描述文档;

2. 能够针对课题中遇到的问题,合作思考解决,算法有一定的创新之处;

课题输出:

1. 算法相关的原始代码及详细的算法描述文档;

2. 算法仿真结果(图片、视频、相关数据指标等);

3. 设计中的问题解决与团队合作过程的心得小结;

第六届中国研究生创芯大赛承办单位介绍

第六届中国研究生创“芯”大赛承办单位华中科技大学坐落于湖北省武汉市,是国家教育部直属重点综合性大学、国家“211工程”重点建设和“985工程”建设高校之一,也是首批“双一流”建设高校。学校校园占地7000余亩,园内树木葱茏,碧草如茵,绿化覆盖率72%,被誉为“森林式大学”。学校师资力量雄厚,并遵循“应用领先、基础突破、协调发展”的科技发展方略,构建起了覆盖基础研究层、高新技术研究层、技术开发层三个层次的科技创新体系。

华中科技大学集成电路学院以服务国家重大战略和区域经济发展为目标,承建集成电路科学与工程和电子科学与技术两个一级学科,电子科学与技术、集成电路设计与集成系统、微电子科学与工程三个国家一流本科专业,先后获批国家集成电路人才培养基地、国家示范性微电子学院、国家集成电路产教融合创新平台。学院按照“国际视野、拔尖示范、协同育人、自主创芯、服务地方"的思路 ,通过人才培养、科学研究、学科建设“三位一体”,充分发挥产教融合优势,支撑和引领华中地区集成电路产业高速发展。

武汉东湖新技术开发区简称东湖高新区,又称中国光谷、简称光谷,于1988年创建成立,是中国首批国家级高新区、第二个国家自主创新示范区、中国(湖北)自由贸易试验区武汉片区,并获批国家光电子信息产业基地、国家生物产业基地、央企集中建设人才基地、国家首批双创示范基地等。 经过30多年的发展,东湖高新区综合实力和品牌影响力大幅提升,知识创造和技术创新能力提升至全国169个国家级高新区第一,成为全国10家重点建设的“世界一流高科技园区”之一。