Cadence企业命题专项奖

Cadence企业命题专项奖专门用于奖励选择Cadence企业命题的赛队,由企业专家评出。Cadence企业命题专项奖是初赛奖,入围决赛的参赛队伍继续参加大赛决赛奖项评比,与初赛奖项互不冲突。

奖项设置

一等奖赛队1支,每队奖金1万元;

二等奖赛队3支,每队奖金5千元;

Cadence赛题交流群

添加秘书处微信cpicic-ctri,备注进入Cadence企业命题交流群

Cadence-创芯大赛人才政策

Cadence公司鼓励技术部门从创芯大赛获奖学生中挖掘人才。在招聘中,获奖学生可以直接进入HR面试环节,或通过Cadence实习直通车,优先为获奖学生提供实习生岗位机会。另外,Cadence公司还可以为在Cadence实习并有志于进一步出国深造的同学提供推荐信(Cadence标准格式化版本)。

Cadence赛题文档下载

https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=b841f5ab31a34ee18c89b8cbc7c98da5

Cadence赛题参考资料

https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=8f37da2b8556492a9b8028dc444ba124

Cadence赛题讲解视频

https://www.bilibili.com/video/BV1yT411q7Ma/

赛题背景:

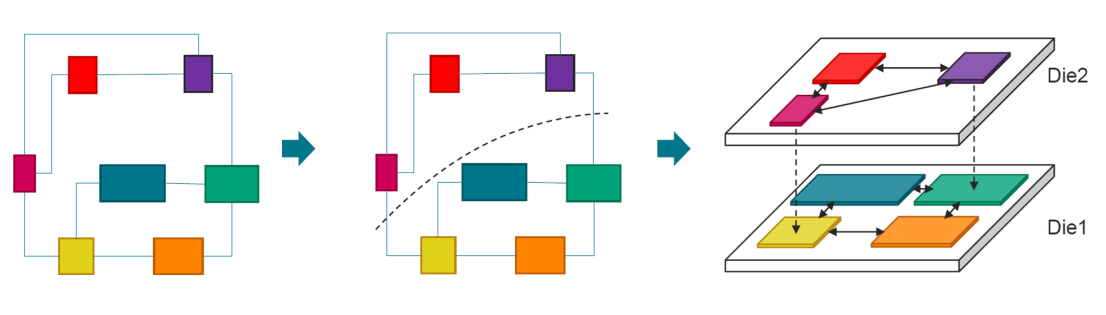

通过对整个大型电路进行合理划分之后,划分后的模块被分配到两个或多个单独的裸片(die)上,并通过三维集成技术使得划分后的模块与模块之间的连接能从二维布线进化为三维布线。

更短的布线距离能带来

能跨越不同制程的die之间的三维连接能带来

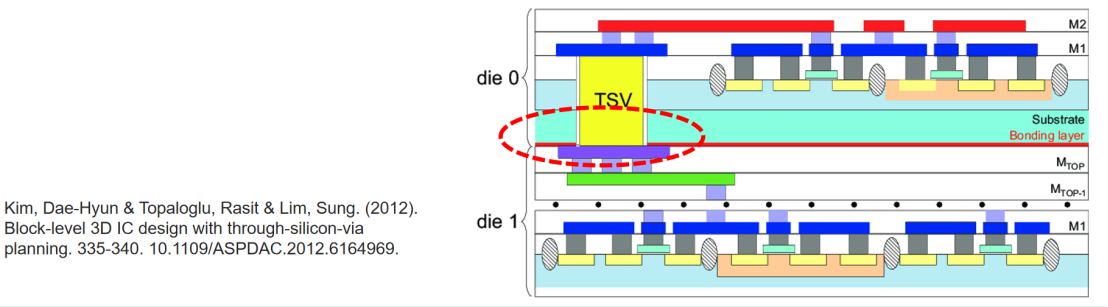

在经过RC抽取的3DIC的架构中,因为跨越die部分的抽取模型的复杂性,会产生额外的数以百万计的寄生电容和电阻, 而直接把这些抽取后的寄生值直接添加到原先的网表中会显著增加机器的负担。因此,在保留原有抽取后特性的基础上的精减算法是十分必要的。

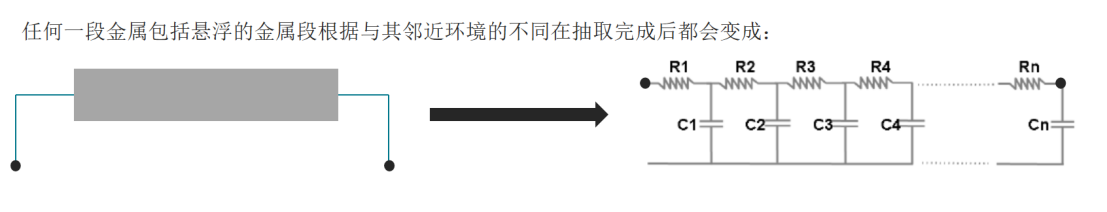

因为半导体制造工艺中需要满足比如metal density的需求,会对芯片的empty region用short metal line进行填充。这些用来填充的金属并不会与任何其他信号网络或地发生连接,因此会产生大量的floating nets,而这些floating nets对于电路本身并无意义,只是单纯在抽取完成后成为电路的负担。

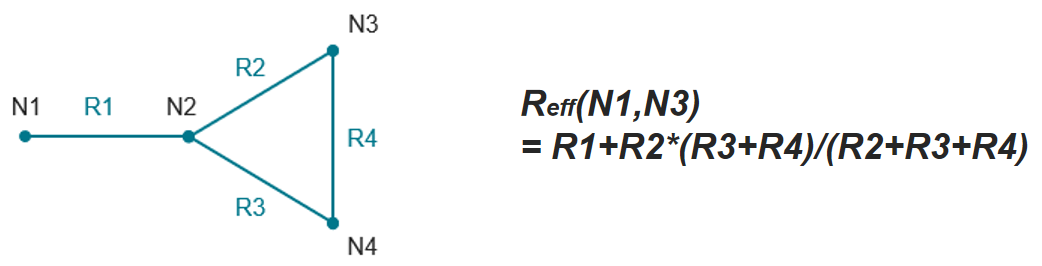

最简单的节点‘N1’到‘N3’的等效电阻能被表述成:

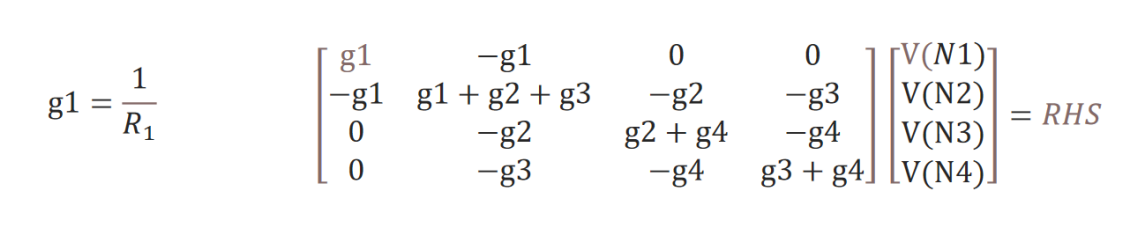

上述电路的矩阵形式:

向量‘right hand side’(‘RHS’)的值取决于想要哪两个节点间的等效电阻

如何高效的计算向量‘V’的估计值,当方程被给定为G⋅V≈RHS

可供参考的算法(仅提供参考使用,不设限制)

等效导体网络(翻译成数学语言)

如何高效计算出向量‘V’在方程G⋅V≈RHS中的估计值,当

悬浮节点在数量级上大于信号节点。

悬浮节点会对信号网络产生影响。

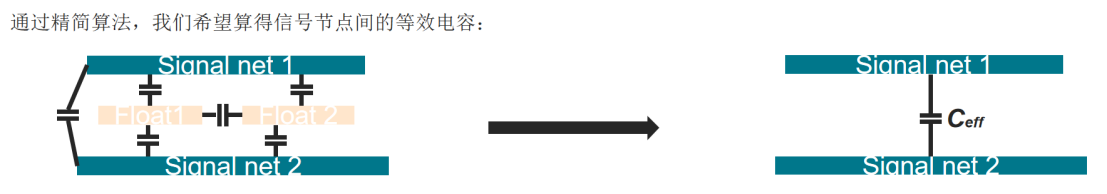

在保留悬浮节点的影响的前提下,需要计算出移除悬浮节点后的等效电容矩阵。

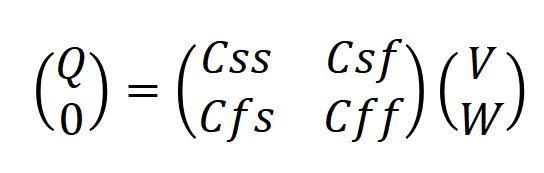

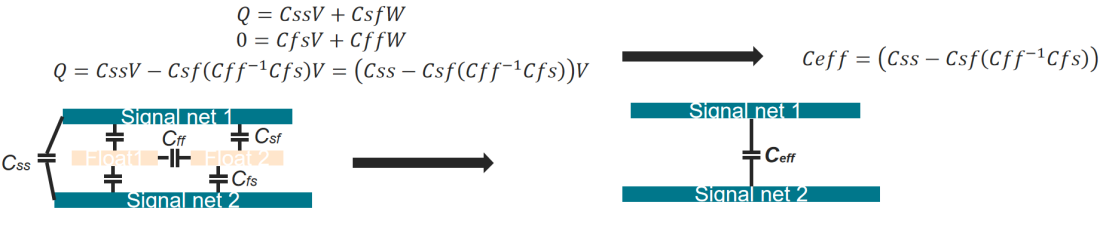

最简单的等效电容矩阵的推导如下:

Q: charge on signal nets

V: voltage on signal nets

W: voltage on floating nets

Css: signal to signal capacitance

Csf,Cfs: floating nets to signal capacitance

Cff: floating nets to floating nets capacitance

计算等效电容矩阵的瓶颈是高效计算出‘Cff^−1’的估计值,当

随着信号沿着导线从一个制程穿越到另一个制程,或不同参数的同一个制程, R&C的抽取会在不同的制程(环境)中展现出不同的dense/sparse特性。

有没有可能把大的矩阵根据density/sparsity的不同而切割成小的子矩阵并分别由不同的算法依照该子矩阵的特性而处理。

P. K. Jo, T. Zheng and M. S. Bakir, "Polylithic Integration of 2.5D and 3D Chiplets Using Interconnect Stitching," 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 2019, pp. 1803-1808, doi: 10.1109/ECTC.2019.00278.

任务

评分标准

加分项:

减分项:

团队某个人承担绝大部分工作量。

关于Cadence

![]()

Cadence 在计算软件领域拥有超过 30 年的专业经验,是电子系统设计产业的关键领导者。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计从概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续八年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站 cadence.com。

第六届中国研究生创芯大赛承办单位介绍

第六届中国研究生创“芯”大赛承办单位华中科技大学坐落于湖北省武汉市,是国家教育部直属重点综合性大学、国家“211工程”重点建设和“985工程”建设高校之一,也是首批“双一流”建设高校。学校校园占地7000余亩,园内树木葱茏,碧草如茵,绿化覆盖率72%,被誉为“森林式大学”。学校师资力量雄厚,并遵循“应用领先、基础突破、协调发展”的科技发展方略,构建起了覆盖基础研究层、高新技术研究层、技术开发层三个层次的科技创新体系。

华中科技大学集成电路学院以服务国家重大战略和区域经济发展为目标,承建集成电路科学与工程和电子科学与技术两个一级学科,电子科学与技术、集成电路设计与集成系统、微电子科学与工程三个国家一流本科专业,先后获批国家集成电路人才培养基地、国家示范性微电子学院、国家集成电路产教融合创新平台。学院按照“国际视野、拔尖示范、协同育人、自主创芯、服务地方"的思路 ,通过人才培养、科学研究、学科建设“三位一体”,充分发挥产教融合优势,支撑和引领华中地区集成电路产业高速发展。

武汉东湖新技术开发区简称东湖高新区,又称中国光谷、简称光谷,于1988年创建成立,是中国首批国家级高新区、第二个国家自主创新示范区、中国(湖北)自由贸易试验区武汉片区,并获批国家光电子信息产业基地、国家生物产业基地、央企集中建设人才基地、国家首批双创示范基地等。 经过30多年的发展,东湖高新区综合实力和品牌影响力大幅提升,知识创造和技术创新能力提升至全国169个国家级高新区第一,成为全国10家重点建设的“世界一流高科技园区”之一。