关于圣邦微电子

圣邦微电子(北京)股份有限公司(股票代码 300661)专注于高性能、高品质模拟集成电路的研发和销售。公司产品覆盖信号链和电源管理两大领域,拥有 30 大类 4600 余款可销售型号,包括高精度运放、低噪声运放、高速运放、低功耗运放、高速比较器、高精度 ADC、大动态背光 LED 驱动、高精度低噪声低压差线性稳压器、各类高效低功耗电源管理芯片、高压大电流锂电池充电管理及电池保护芯片、多种类型的高功率马达驱动芯片、氮化镓(GaN)晶体管驱动器、功率 MOSFET,以及各类车规芯片等。产品性能和品质对标世界一流模拟芯片厂商同类产品,部分关键性能指标有所超越,广泛应用于工业、汽车电子、通信设备、消费类电子和医疗仪器等领域,以及物联网、新能源和人工智能等新兴市场。

公司技术团队由国际行业资深专家组成,拥有先进的模拟集成电路设计、工艺、测试技术和丰富的生产管理、品质管理经验,核心人员平均从业年龄超过二十年。公司全部产品自主研发,拥有百分之百自主知识产权,多项产品获得北京市科学技术奖、中国半导体创新产品和技术奖、“中国芯”优秀产品奖、北京市专利奖等荣誉。展望未来,公司将继续厚积薄发,推陈出新,致力成为世界模拟芯片行业的领跑者。

关于圣邦微电子企业命题

圣邦微电子企业命题专项奖专门用于奖励选择圣邦微电子企业命题的赛队,由企业专家评出。圣邦微电子企业命题专项奖是初赛奖,入围决赛的参赛队伍继续参加大赛决赛奖项评比,与初赛奖项互不冲突。

圣邦微电子企业命题奖项设置

圣邦微电子企业命题一等奖:1支队伍,每队奖金 1 万元;

圣邦微电子企业命题二等奖:3支队伍,每队奖金 5 千元;

圣邦微电子-创芯大赛人才政策

圣邦微电子始终鼓励业务部门培养优秀工程人才,从创芯大赛中发掘未来之星。具体招聘政策正在制定中,请留意大赛最新消息。

赛题一:基于CMOS工艺的带隙基准电压源设计

一、背景

带隙基准电压源(Bandgap Reference Circuit)是模拟集成电路中的核心模块,可为ADC、DAC、LDO等电路提供与温度、电源电压无关的稳定参考电压。其核心原理是通过对双极性晶体管(BJT)的正温度系数电压(PTAT)和负温度系数电压(CTAT)进行加权求和,实现近似零温度系数的输出电压(约1.2V或其它值需要公式理论支撑)。

二、设计任务

本题目要求参赛者设计一个满足工业级性能指标的带隙基准电压源。

三、设计指标

四、设计建议

五、考核内容

六、设计文档要求

七、评分标准(权重)

|

项目 |

权重 |

说明 |

|

设计思路 |

30% |

架构合理性、公式推导完整性、关键参数选择依据(如BJT比例) |

|

仿真结果 |

40% |

指标是否达标、工艺角覆盖全面性、仿真结果的可信度 |

|

文档与PPT |

20% |

逻辑清晰、图文并茂、仿真Testbench说明 |

|

创新与加分项 |

10% |

曲率补偿、低噪声设计、面积优化等 |

八、提交要求

设计报告(PDF或PPT格式):包含原理图、公式推导、仿真结果与分析。

注:本题综合考察参赛者对模拟电路设计流程的掌握,鼓励通过文献调研优化设计,培养工程思维!

赛题二:高边电流检测放大电路设计

一.背景介绍

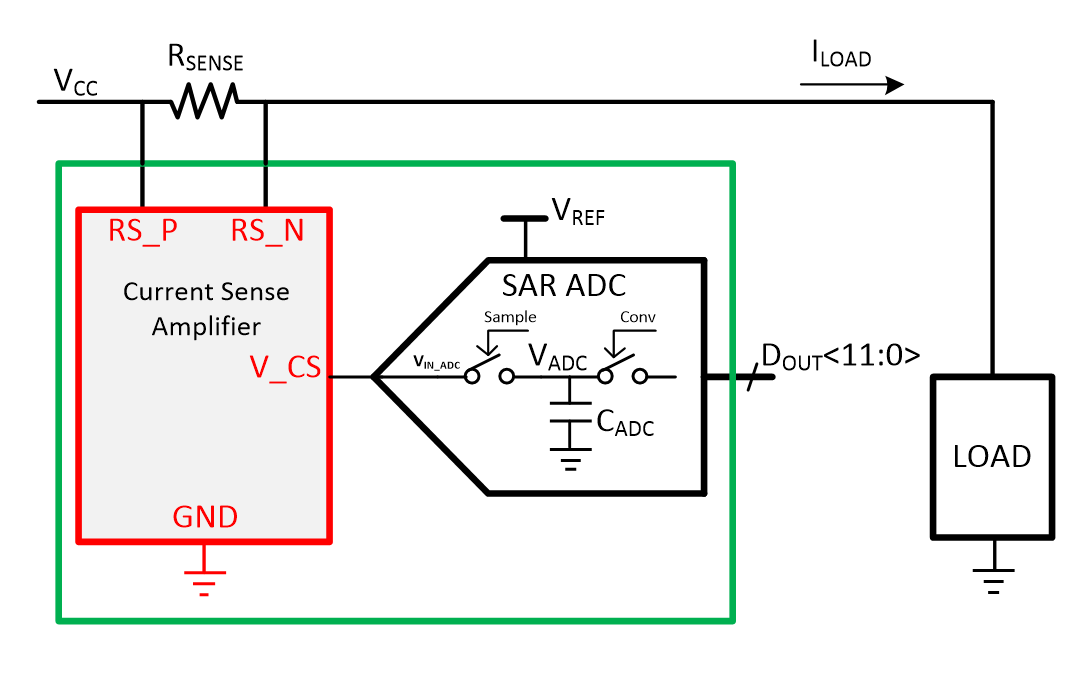

电流检测是在实际中有着广泛应用的关键技术,通过实时检测负载电流,可以优化提升系统效率和防止电路过载。如图所示的高边电流检测在电源(VCC)和负载之间串联一个低阻值的检测电阻RSENSE形成一个小的电压降,这个压降被进一步线性放大成为一个正比于负载电流ILOAD的对地电压信号V_CS,通过ADC采样转换得到相应的数字化输出。

二.设计要求

本赛题要求设计一个完整的用于高边电流检测的放大电路(图中红色部分),其接口描述如下:

|

Name |

Function |

|

RS_P |

Current sense amplifier positive input |

|

RS_N |

Current sense amplifier negative input |

|

V_CS |

Current sense amplifier output |

|

GND |

Ground |

设计和仿真中,VCC可采用理想电压源, SAR ADC不在设计范围之内,可简化为一个理想开关串联输入采样电容作为电流检测放大电路的负载。除此之外,设计中无其它输入,也不应出现其它理想元器件。

|

Parameters |

Min |

Typ |

Max |

Unit |

Comments |

|

RSENSE |

|

0.01 |

|

ohm |

|

|

VCC |

6 |

|

30 |

V |

|

|

ILOAD |

0.01 |

|

20 |

A |

|

|

Input Common Mode Voltage range |

6 |

|

30 |

V |

|

|

Input Offset Voltage |

|

|

1 |

mV |

关键性能指标1 |

|

Current Sense Accuracy |

|

|

0.5 |

% |

关键性能指标2 |

|

Common Mode Rejection |

100 |

|

|

dB |

关键性能指标3 |

|

Power Supply Rejection |

100 |

|

|

dB |

关键性能指标4 |

|

Total Output Noise |

|

|

100 |

uV |

关键性能指标5 |

|

Total Current Consumption |

|

|

1 |

mA |

关键性能指标6 |

|

Temperature |

-40 |

|

125 |

℃ |

|

ADC不在设计范围之内,但所设计的电路输出需要能正确驱动如图所示的理想单端输入12-bit SAR ADC,采样开关的电阻可忽略不计,ADC的参数如下:

|

Parameters |

Min |

Typ |

Max |

Unit |

Comments |

|

VIN_ADC |

0 |

|

VREF |

V |

ADC single-ended input voltage range |

|

VREF |

|

1.2 |

|

V |

ADC reference voltage |

|

TSample |

|

250 |

|

ns |

ADC sampling time |

|

Sampling Rate |

|

1 |

|

MSPS |

ADC sampling rate |

|

CADC |

|

10 |

|

pF |

ADC sampling capacitance |

四.文档要求

1.系统设计文档

根据设计要求设计系统框图,合理划分子模块,分析和计算相应子模块的设计指标,如有参考文献引用或对比请标明出处。

2.电路原理图

合理规划电路层级对应系统设计和子模块划分,电路原理图应具有可读性,标注关键电路参数和器件参数。

3.电路仿真结果

包含仿真test-bench说明和必要的仿真结果, 电路仿真需覆盖工艺角和温度变化,仿真的目的和结果应当和系统设计文档的相关内容对应。

4.版图的floor plan

不需要·完成版图设计。完成设计电路的floor plan,合理估算版图面积(关键性能指标7)。

五.评分标准

1. 完成设计要求,具有高边电流检测的功能,提供完整的设计文档和仿真结果。(60%)

2. 关键性能指标和电路创新。(40%)

一、背景

本设计需为前序项目中的带隙基准电压源(BGR)提供高驱动能力的输出缓冲级,要求运放能在宽电源电压范围内稳定工作,并具备驱动大容性负载、高精度调节及输出电流保护能力,确保与BGR系统的兼容性。

二、设计指标

三、考核内容

电路原理图:标注输出级尺寸、限流电路、补偿网络及偏置细节。

参考文献:至少引用2篇高精度运放或BGR驱动设计论文。

四、评分标准(权重)

|

项目 |

权重 |

说明 |

|

设计合理性 |

30% |

输出级电流能力、限流实现、低静态功耗策略 |

|

仿真完备性 |

40% |

Line/Load Regulation覆盖性、容性负载稳定性、多电压验证。 |

|

文档与创新 |

20% |

公式推导严谨性、结果对比分析深度、创新补偿方案。 |

|

难点突破 |

10% |

47 μF负载驱动、75 dB PSRR达成、多电压兼容性优化。 |

五、提交要求

设计报告(PDF):需包含原理图、公式推导、仿真结果及多电压分析。