圣邦微电子赛题专项奖设置:

圣邦企业命题专项奖专门用于奖励选择圣邦企业命题的赛队,圣邦企业命题专项奖是初赛奖,由企业专家评出。入围决赛的参赛队伍继续参加大赛决赛奖项评比,与初赛奖项互不冲突。

圣邦专项奖设:

圣邦赛题文档下载:

https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=723ef8444d9d4384bceb7a312fce95e6

圣邦赛题答疑邮箱:

Campus@sg-micro.com

圣邦-创芯大赛人才政策:

圣邦微电子鼓励并且期望技术及业务部门从创芯大赛中发掘优秀人才,并为他们提供优先录用的机会。获得全国二等奖及以上的同学,将给予面试直通卡,即免笔试,由资深技术专家直接面试。

圣邦赛题视频讲解:

赛题一:16Gbps线性转接驱动器设计

https://www.bilibili.com/video/BV1XC41137K9/?share_source=copy_web

赛题二:快速锁定的低噪声晶振电路

https://www.bilibili.com/video/BV1Z1421d7Xn/?share_source=copy_web&vd_source=731983d24066c046753f8a80d7ad6bd5

赛题一:16Gbps线性转接驱动器设计

一、背景介绍

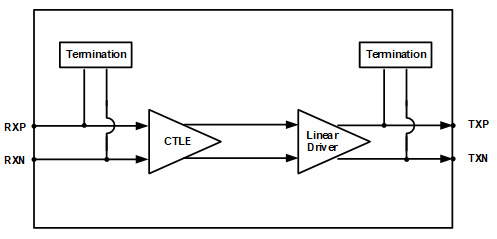

线性转接驱动器(Linear Redriver),集成了连续时间线性均衡器(CTLE, Continuous Time Linear Equalizer)来提供高频的增益补偿,从而减小或者消除信道引入的码间干扰(Inter Symbol Interference, ISI)。

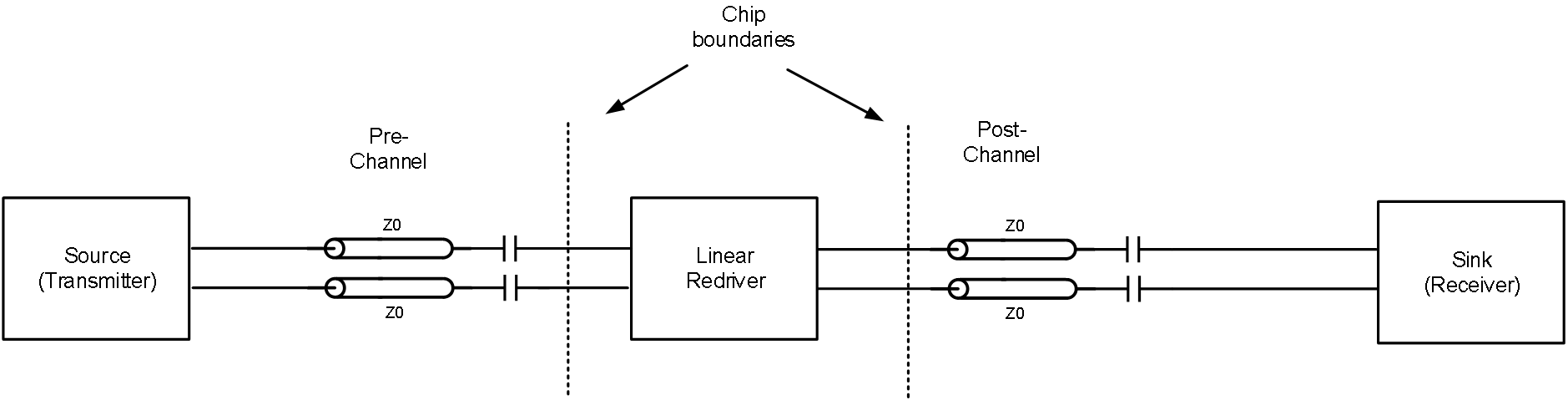

线性转接驱动器(Linear Redriver)的典型应用如下,其可以补偿高速信号通过Pre-channel之后的高频衰减,从而在线性转接驱动器的输出获得较好的眼图输出。

二、设计指标

请设计一款16Gbps线性转接驱动器。该驱动器需满足以下指标:

|

Parameter |

Min |

Typ |

Max |

Unit |

Comments |

|

Power Supply, VDD |

|

VDD |

|

V |

VDD depends on process node |

|

Operating Temperature |

-40 |

|

85 |

℃ |

|

|

Electrical spec for receiver |

|||||

|

R_rx_diff |

|

100 |

|

ohm |

RX differential impedance |

|

V_rx_term |

|

0 |

|

V |

Receive termination voltage |

|

V_rx_pp |

|

0.6 |

0.8 |

V |

Differential peak to peak input voltage |

|

Equalizer gain |

0 |

|

18 |

dB |

@ 8G Hz Maximum gain is 18dB Minimum gain is 0dB Adjustable, 1.2dB/step |

|

RL_rx_diff |

|

-12 |

|

dB |

Differential return loss in RX, DC to 8GHz |

|

RL_rx_cm |

|

-10 |

|

dB |

Common mode return loss in RX, DC to 8GHz |

|

Gain_lf_var |

-2 |

0 |

2 |

dB |

Low frequency voltage gain variation over PVT for 0dB setting |

|

Gain_hf_var |

-2.5 |

|

2.5 |

dB |

EQ boosting gain variation over PVT |

|

Electrical spec for transmitter |

|||||

|

R_tx_diff |

|

100 |

|

ohm |

TX differential impedance |

|

RL_tx_diff |

|

-12 |

|

dB |

Differential return loss in TX, DC to 8GHz |

|

RL_tx_cm |

|

-10 |

|

dB |

Common mode return loss in TX, DC to 8GHz |

|

V_tx_cm |

|

|

VDD |

V |

Transmitter termination voltage |

|

V_tx_pp |

|

0.6 |

0.8 |

V |

Differential peak to peak output voltage |

|

JIT_data |

|

7 |

|

ps |

Additive total jitter with data. 16Gbps, PRBS15, 800mVpp input swing |

三、设计建议和文档要求

1、设计建议

2、文档要求

四、评分标准

|

|

内容 |

分值 |

评分标准 |

|

基本指标考核 |

电路指标 |

40分 |

|

|

版图质量 |

10分 |

|

|

|

设计完整性 |

10分 |

|

|

|

优化指标考核 |

|

20分 |

|

|

文档及答辩 |

文档 |

10分 |

|

|

答辩 |

10分 |

|

|

|

附加指标考核 |

|

20分 |

|

五、补充内容

1、工艺角描述

2、仿真条件

赛题二: 快速锁定的低噪声晶振电路

一、背景介绍

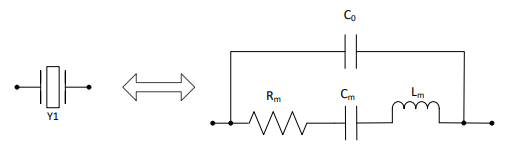

晶体简化模型如下,由R-L-C器件组成,设计需要的模型参数可以在设计指标中获得。

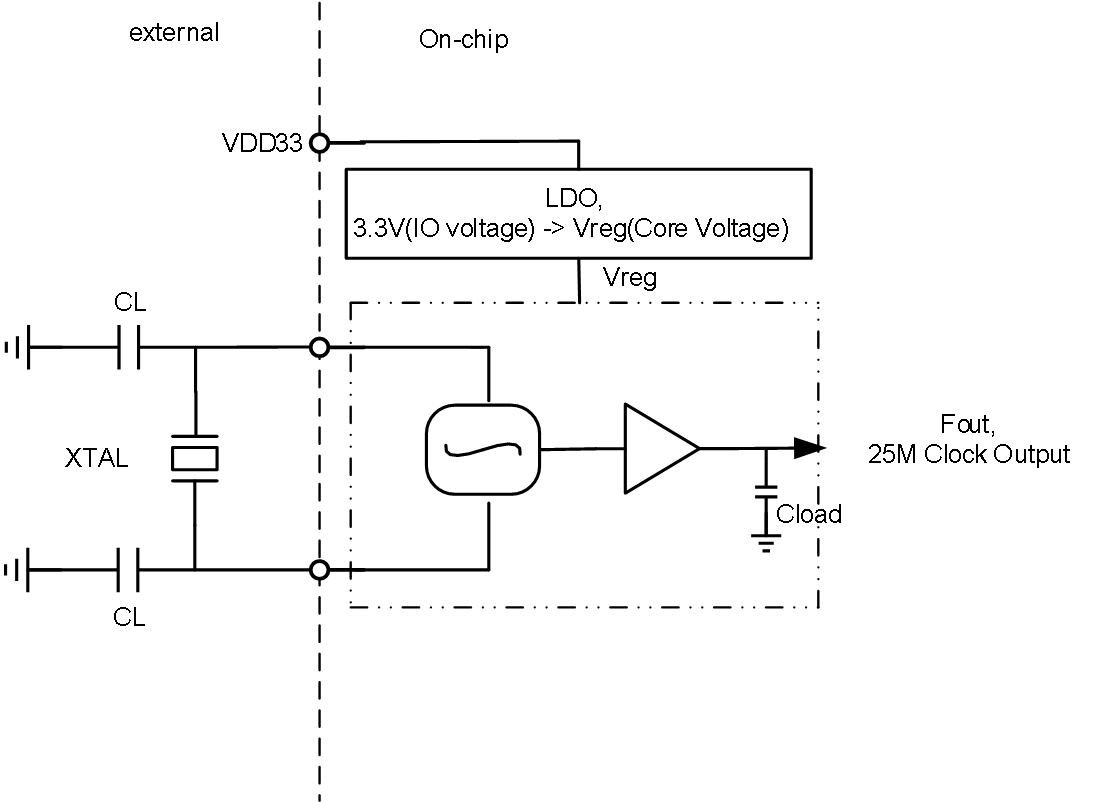

晶振电路的整体框图如下,左侧是片外的晶体以及电容,右侧是片上的有源电路。

二、设计指标

请设计一款快速锁定的低噪声晶振电路,该电路需要满足以下指标:

|

Parameter |

Min |

Typ |

Max |

Unit |

Comments |

|

Power Supply, VDD33 |

|

3.3 |

|

V |

IO voltage |

|

Operating temperature |

-40 |

|

125 |

℃ |

|

|

XTAL osc frequency |

|

25 |

|

MHz |

|

|

Clock frequency accuracy |

-50 |

|

50 |

ppm |

Here assume XTAL’s accuracy is +/-30ppm, need consider about active circuit induced frequency error |

|

Startup time |

|

|

1 |

ms |

|

|

Power |

|

|

2 |

mW |

|

|

Duty cycle |

45 |

|

55 |

% |

@ output |

|

Output swing @ Fout |

|

Vreg |

|

V |

Single ended, @ output, Vreg depends on process node, Cload=100fF |

|

Quartz resonator parameters |

|||||

|

Rm |

|

|

60 |

ohm |

|

|

Cm |

|

2.04 |

|

fF |

|

|

Lm |

|

19.87 |

|

mH |

|

|

C0 |

|

0.62 |

|

pF |

|

|

CL, crystal load capacitance |

|

12 |

|

pF |

|

|

Output clock phase noise mask |

|||||

|

PN: 100Hz offset |

|

|

-95 |

dBc/Hz |

|

|

PN: 1KHz offset |

|

|

-125 |

dBc/Hz |

|

|

PN: 10KHz offset |

|

|

-133 |

dBc/Hz |

|

|

PN: 100KHz offset |

|

|

-140 |

dBc/Hz |

|

|

PN: 1MHz offset |

|

|

-145 |

dBc/Hz |

|

|

PN: 10MHz offset |

|

|

-148 |

dBc/Hz |

|

三、 设计建议和文档要求

1、设计建议

1)LDO输出Vreg给XTAL的起振电路及输出Buffer供电;

2)Vreg的数值与工艺选取及设计优化相关;

2、文档要求

四、 评分标准

|

|

内容 |

分值 |

评分标准 |

|

基本指标考核 |

电路指标 |

40分 |

|

|

版图质量 |

10分 |

|

|

|

设计完整性 |

10分 |

|

|

|

优化指标考核 |

|

20分 |

|

|

文档及答辩 |

文档 |

10分 |

|

|

答辩 |

10分 |

|

|

|

附加指标考核 |

|

20分 |

|

五、补充内容

1、工艺角描述

2、仿真条件

第七届中国研究生创芯大赛承办单位介绍

第七届中国研究生创“芯”大赛承办单位华中科技大学坐落于湖北省武汉市,是国家教育部直属重点综合性大学、国家“211工程”重点建设和“985工程”建设高校之一,也是首批“双一流”建设高校。学校校园占地7000余亩,园内树木葱茏,碧草如茵,绿化覆盖率72%,被誉为“森林式大学”。学校师资力量雄厚,并遵循“应用领先、基础突破、协调发展”的科技发展方略,构建起了覆盖基础研究层、高新技术研究层、技术开发层三个层次的科技创新体系。

华中科技大学集成电路学院以服务国家重大战略和区域经济发展为目标,承建集成电路科学与工程和电子科学与技术两个一级学科,电子科学与技术、集成电路设计与集成系统、微电子科学与工程三个国家一流本科专业,学院是全国同时拥有国家集成电路学院、国家集成电路产教融合创新平台、国家示范性微电子学院、国家集成电路人才培养基地、微电子学与固体电子学国家重点学科等集成电路领域五大国家级人才培养学科平台的6所高校之一。学院按照“国际视野、拔尖示范、协同育人、自主创芯、服务地方"的思路 ,通过人才培养、科学研究、学科建设“三位一体”,充分发挥产教融合优势,支撑和引领华中地区集成电路产业高速发展。

武汉东湖新技术开发区简称东湖高新区,又称中国光谷、简称光谷,于1988年创建成立,是中国首批国家级高新区、第二个国家自主创新示范区、中国(湖北)自由贸易试验区武汉片区,并获批国家光电子信息产业基地、国家生物产业基地、央企集中建设人才基地、国家首批双创示范基地等。 经过30多年的发展,东湖高新区综合实力和品牌影响力大幅提升,知识创造和技术创新能力提升至全国169个国家级高新区第一,成为全国10家重点建设的“世界一流高科技园区”之一。