关于华大九天

北京华大九天科技股份有限公司(简称“华大九天”)成立于2009年,一直聚焦于EDA工具的开发、销售及相关服务业务,致力于成为全流程、全领域、全球领先的EDA提供商。

华大九天主要产品包括模拟电路设计全流程EDA工具系统、存储电路设计全流程EDA工具系统、射频电路设计全流程EDA工具系统、数字电路设计EDA工具、平板显示电路设计全流程EDA工具系统、晶圆制造EDA工具和先进封装设计EDA工具等软件,并围绕相关领域提供技术开发服务。产品和服务主要应用于集成电路设计、制造及封装领域。

华大九天总部位于北京,在南京、成都、深圳、上海、香港、广州、北京亦庄和西安等地设有全资子公司,在武汉、厦门等地设有分支机构。

华大九天企业命题专项奖

华大九天企业命题专项奖专门用于奖励选择华大九天企业命题的赛队,由企业专家评出。华大九天企业命题专项奖是初赛奖,入围决赛的参赛队伍继续参加大赛决赛奖项评比,与初赛奖项互不冲突。

华大九天企业命题奖项设置

华大九天企业命题一等奖2支队伍,每队奖金 1 万元;

华大九天企业命题二等奖6支队伍,每队奖金 5 千元。

华大九天-创芯大赛人才政策

北京华大九天科技股份有限公司希望从创芯大赛获奖团队中发现人才,挖掘人才,并在招聘中提供快速通道。参加创芯大赛的获奖学生,投递研发类岗位:1. 获全国二等奖三等奖学生,可以免笔试直接进入技术面试;2. 获一等奖及以上学生,可直接进入综合面试;3. 华大九天企业专项奖等级等同全国奖对应等级待遇。

赛题一:全差分放大器的设计

*赛题所需软件及PDK报名后申请获得,请进赛题交流群获取最新通知及操作指南。申请表下载链接:https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=3953952990d84b8c84ce31ec6d0cb124

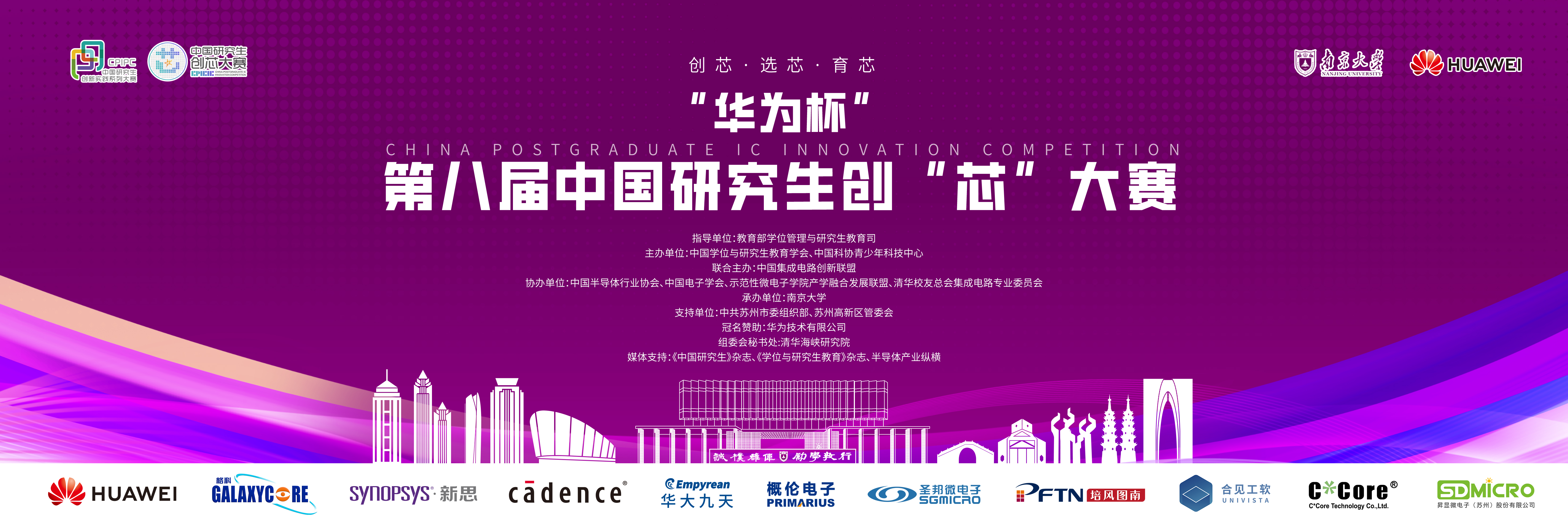

题目:采用华大九天Aether全定制IC设计平台及其自带的0.13um openPDK,设计一款全差分放大器电路,完成从原理图设计直至后仿真的过程。可参考以下架构:

工作条件:

1.采用给定0.13um openPDK工艺,需要完全采用PDK库中提供的器件完成设计;需设计Bandgap模块提供偏置电流或偏置电压;

2.以下指标工作于电源电压1.6~2.0V(Nominal 1.8V),温度-20~80℃(Nominal 27℃),工艺corner包括SS/TT/FF;

要求技术指标(均考虑所有PVT corner组合中的最差后仿真值):

1.提交全部原理图(含运放主电路及Bandgap电路等)、版图和前、后仿真的设置等数据(5分);

2.放大器开环DC增益Av0≥80dB,-3dB带宽BW0≥3MHz,开环相位裕度PhaseMargin≥50°,给出测试电路testbench和后仿真结果(20分);

3. 1MHz时电源抑制比PSRR-1M≥90dB;给出PSRR测试电路和仿真结果(10分)

4.噪声要求:工作于1MHz闭环工作、闭环放大倍数为40dB时,使用HBNoise仿真,在区间10kHz~100MHz内的RMS差分输出噪声值≤10nV2/Hz,其中用于实现闭环连接的外部器件可使用理想无噪声器件;给出噪声测试电路和仿真结果(15分);

5. 运放正常工作电流(En=1),IDC≤5mA;给出测试电路和仿真结果(5分);

6. 运放关断电流(En=0),Idown≤100nA;给出测试电路和仿真结果(5分);

7. 整体版图清晰、直观、简洁,有适当的差分匹配设计和Guardring设计(10分);

8. 完成物理验证,DRC和LVS结果均clean(10分,有一处DRC或LVS错误扣1分,直至扣完为止);

9. 提供Word版设计报告,详细阐述设计思路和设计过程、仿真结果(20分)。

赛题二:振荡器的设计

*赛题所需软件及PDK报名后申请获得,请进赛题交流群获取最新通知及操作指南。申请表下载链接:https://cpipc.acge.org.cn/sysFile/downFile.do?fileId=3953952990d84b8c84ce31ec6d0cb124

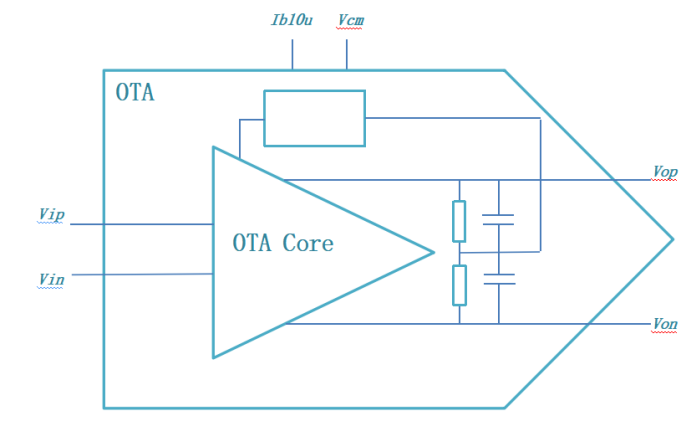

题目:采用华大九天Aether全定制IC设计平台及其自带的openPDK,设计一款压控振荡器(VCO)电路,完成全部电路图设计和仿真的过程。参考以下架构:

可参考以下架构:

工作条件:

1.采用给定0.13um openPDK工艺,需要完全采用PDK库中提供的器件完成设计;需设计Bandgap模块提供偏置电流或偏置电压;

2.以下指标工作于电源VDD的电压1.6~2.0V(Nominal 1.8V),温度-20 ~80℃(Nominal 27℃),工艺corner包括SS/TT/FF;

要求技术指标(考虑所有PVT corner组合中最差后仿真值):

1.提交全部原理图(含振荡主电路及Bandgap电路等)、版图和前、后仿真的设置等数据(5分);

2.输出为差分方波或正弦波,当VTune调节范围在[0.3V,VDD-0.3V],对应输出频率范围需要包含[200MHz,1GHz],给出以0.1V为步进的V-F曲线(可以单调上升或下降,但不能出现拐点)(10分)

3.RMS噪声指标:在输出频率为1GHz时,使用HBNoise分析,得到差分RMS输出相噪指标:

a) ≤-50dBc/Hz @ 10kHz;

b) ≤-75dBc/Hz @ 100kHz;

c) ≤-100dBc/Hz @ 1MHz;

给出测试电路和仿真结果(20分)

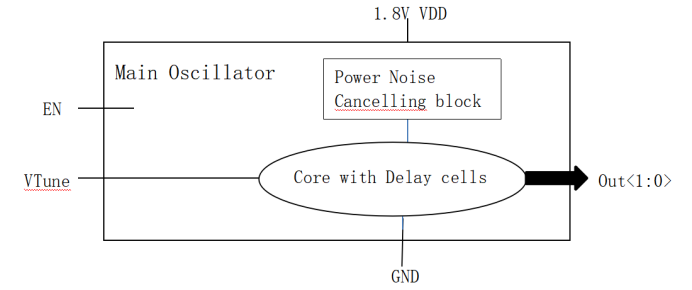

4.Deterministic噪声指标:在输出频率为1GHz时,当VDD以100ps边沿向下跳动50mV,求瞬态差分输出周期变化的差值范围在[0.99ns,1.01ns]之内,即周期变化不超过±1%;给出测试电路和仿真结果(15分);

5. VCO正常工作电流(En=1),IDC≤5mA;给出测试电路和仿真结果(5分);

6. VCO关断电流(En=0),Idown≤100nA;给出测试电路和仿真结果(5分);

7. 整体版图清晰、直观、简洁,有适当的差分匹配设计和Guardring设计(10分);

8. 完成物理验证,DRC和LVS结果均clean(10分,有一处DRC或LVS错误扣1分,直至扣完为止);

9. 提供Word版设计报告,详细阐述设计思路和设计过程、仿真结果(20分)。