关于cadence

Cadence是电子系统设计领域的关键领导者,拥有超过30年的计算软件专业积累。基于公司的智能系统设计战略,Cadence致力于提供软件、硬件和IP产品,助力电子设计概念成为现实。

Cadence的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。

Cadence已连续十年名列美国财富杂志评选的100家最适合工作的公司。

Cadence命题专项奖

Cadence企业命题专项奖专门用于奖励选择Cadence企业命题的赛队,由企业专家评出。Cadence企业命题专项奖是初赛奖,入围决赛的参赛队伍继续参加大赛决赛奖项评比,与初赛奖项互不冲突。

奖项设置

Cadence企业命题一等奖:1 支队伍,每队奖金 1 万元;

Cadence企业命题二等奖:4 支队伍,每队奖金 5 千元;

Cadence-创芯大赛人才政策

Cadence公司鼓励技术部门从创芯大赛获奖学生中挖掘人才。在招聘中,获奖学生可以直接进入HR面试环节,或通过Cadence实习直通车,优先为获奖学生提供实习生岗位机会。另外,Cadence公司还可以为在Cadence实习并有志于进一步出国深造的同学提供推荐信(Cadence标准格式化版本)。

报名链接(大赛官网)

https://cpipc.acge.org.cn/cw/hp/10

参赛说明

https://cpipc.acge.org.cn//cw/detail/10/2c90801795a92a850195cc477e8519c6

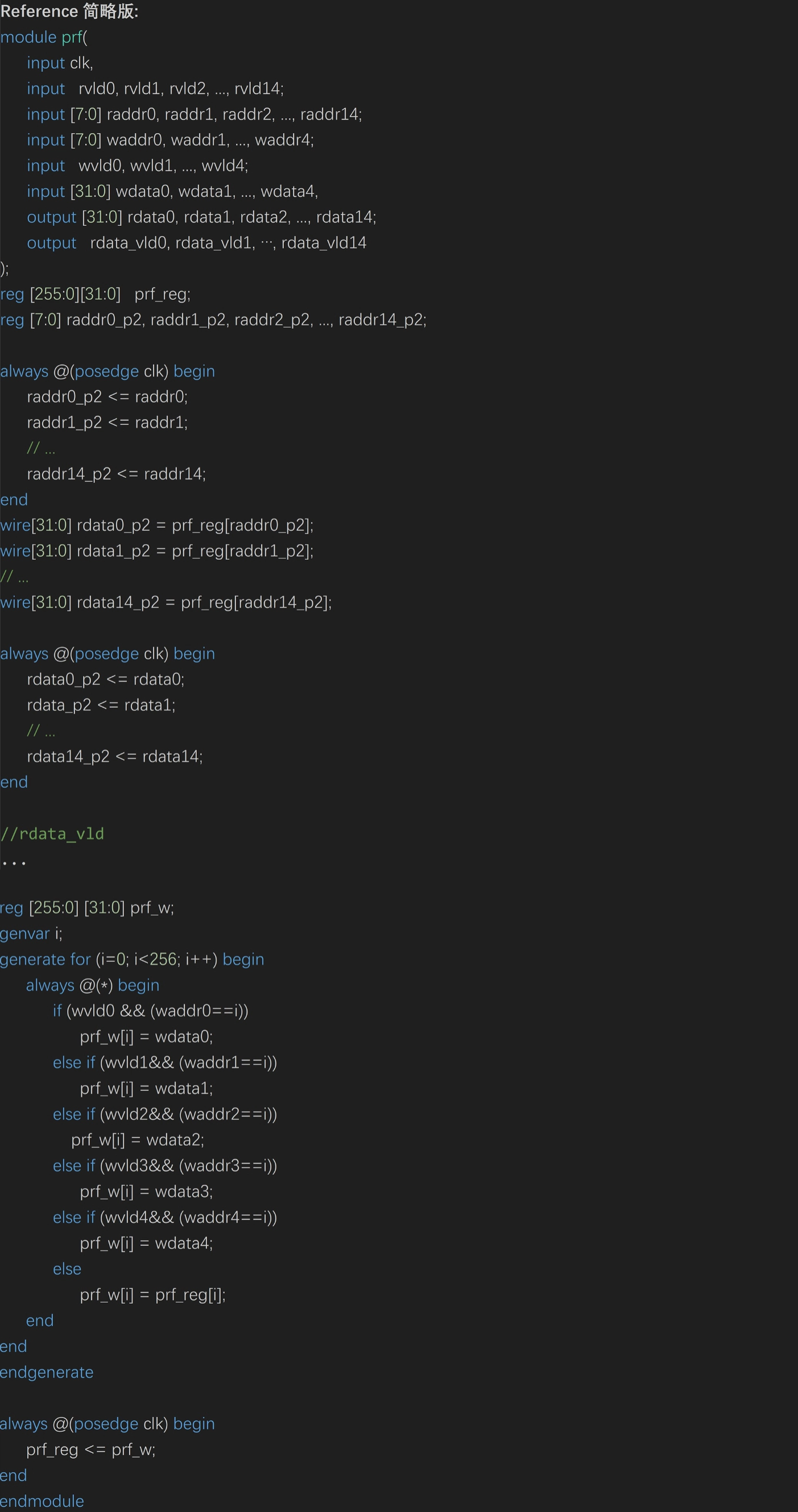

赛题:高性能寄存器文件(Register File)硬件设计

CPU中的寄存器文件(Register File)是存储临时数据和指令执行过程中相关数据的关键组件,它在CPU架构中扮演着至关重要的角色,其设计效率直接影响CPU的整体性能表现。

以RISC-V架构的超标量、乱序执行高性能CPU为例,通过寄存器重命名技术有效解决了多条指令并行执行时产生的WAW、WAR数据冒险问题,该解决方案需要在CPU中实现一个容量大于逻辑寄存器堆的物理寄存器堆。针对寄存器堆的具体实现,可根据不同功能需求选择基于DFF的设计、现有SRAM模块的集成方案,或采用特定的定制化寄存器架构。其中,基于DFF实现的寄存器堆通常由多个寄存器单元及其配套的读写控制逻辑电路构成。在设计DFF构成的多端口读写寄存器堆时,其读写选择控制逻辑面临诸多技术挑战,主要表现为信号延迟较高、电路布线复杂等问题。

对于追求极致性能的CPU架构,寄存器堆设计必须同时满足高性能、低延迟和高并行处理能力等要求。

实现一个支持多端口同时读写且容量大小为256*32bit的高性能寄存器堆(Register File)硬件设计。

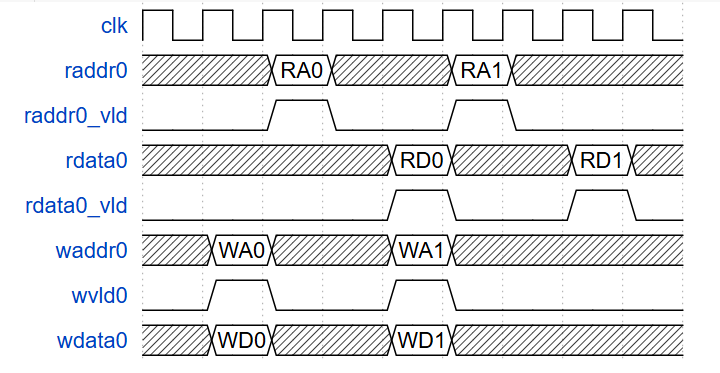

参考时序图

*对于所有选择Cadence 企业命题的学生,如果无法在学校便捷地获得以下参赛工具,可在报名参赛后通过申请获得,申请要求及方式详见链接:

https://kdocs.cn/l/cbs4IisRzKzB

(1)仿真工具Xcelium:

RTL级仿真

门级仿真

simvision debug波形支持

(2)综合工具Genus:

逻辑综合

物理综合

(3)Power计算工具Joules:

支持两种计算power的方式

(a) RTL stimulus + gate database

(b) gate stimulus + gate database

(4)Ispatial工具Innovus:

支持Genus在做综合时,调用Innovus执行Ispatial过程

|

|

项目 |

细则 |

分数 |

|

设计报告 |

设计 |

模块设计合理,逻辑清晰,描述清晰。 |

10 |

|

功能验证报告 |

功能 |

功能验证正确 |

10 |

|

综合报告 |

PPAC (performance, power, area, timing) |

High performance: 提交综合结果以及PPAC报告。根据设计的PPAC结果给予打分,详情查看评分标准。 |

70 |

|

Power详细报告 |

功耗 |

提交activity反标率报告,详细的power报告(包括glitch power) |

10 |

|

加分项 |

工具 |

(1)提交书写规范,设置清晰,PPAC优化设置合理的综合脚本。提出Genus/Innovus工具功能改进的有效建议 |

10 |

|

(2)提交两种计算power的flow,以及计算结果。提出Joules工具功能改进的有效建议 |

10 |

附:

1. 评分标准

(1) 设计的congestion必须满足以下条件:

overflow H: <3%

overflow V: <3%

max hotspot: <1000

(2) PPA各自评分权重如下:

Per_weight: 0.52

Area_weight: 0.24

Power _weight: 0.24

(3) 提交报告时需要提交下表:

|

Performance (unit Mhz) |

Area (unit µm²) |

Power (unit mW) |

|

|

|

|

(4) 会把提交上来的报告根据PPA的数据排名,根据排名给予不同的计分比率

|

Per/Area/Power排名百分比(%) |

Ration1 |

Ration2 |

Ration3 |

|

0-5 |

1 |

1 |

1 |

|

5-15 |

0.8 |

0.8 |

0.8 |

|

15-30 |

0.6 |

0.5 |

0.5 |

|

30-50 |

0.4 |

0.5 |

0.5 |

|

50-70 |

0.2 |

0.2 |

0.2 |

|

70-100 |

0.1 |

0.1 |

0.1 |

(5) 综合报告部分总分计算公式:

Score = (Per_weight*Ration1 + Area_weight *Ration2 + Power_weight *Ration3) *70

注:如果出现分数一样的情况,优先按照performance进行排名,其次是power,最后是area。

2. SDC文件

#clock frequency

create_clock -name $clk_name -period $clk_period [get_ports clk]

#max transition

set_max_transition 0.6

#max fanout

set_max_fanout 32

3. Process Design Kit下载地址

4.赛题答疑&交流群

添加大赛秘书微信备注cadence,进入微信赛题答疑交流群。