关于概伦电子

概伦电子(688206.SH)是国内首家EDA上市公司、关键核心技术具备国际市场竞争力的EDA领军企业,致力于打造应用驱动的、覆盖集成电路设计与制造的EDA全流程解决方案,支撑各类高端芯片研发的持续发展,并联合产业链上下游和EDA合作伙伴,建设有竞争力和生命力的EDA生态;通过EDA方法学创新,推动集成电路设计和制造的深度联动,加快工艺开发和芯片设计进程,提高集成电路产品的良率和性能,增强集成电路企业整体市场竞争力。

概伦电子赛题专项奖设置:

说明:概伦电子赛题专项奖专门用于奖励选择概伦电子赛题的获奖赛队。概伦电子专项奖是初赛奖,参赛赛队可同时参加大赛执行委员会组织的其他大赛奖项的评审和获奖。

概伦电子-创芯大赛人才招聘政策:

概伦电子公司鼓励和支持技术部门从创芯大赛获奖学生中挖掘人才。在校招过程中,本次创芯大赛获奖学生可以跳过笔试,直接进入面试环节,概伦电子公司将优先为获奖学生提供岗位实习的机会。

报名链接(大赛官网)

https://cpipc.acge.org.cn/cw/hp/10

参赛说明

https://cpipc.acge.org.cn//cw/detail/10/2c90801795a92a850195cc477e8519c6

VeriSim是一款先进的逻辑仿真器,提供全面的数字设计验证解决方案,覆盖系统级、行为级、RTL级和门级数字电路仿真验证的需求。配备高性能的仿真引擎和约束求解器,旨在提高编译时效率,并确保设计的正确性和稳定性;可适配众多主流硬件描述语言,包括Verilog、VHDL、SystemVerilog、SystemC 等,以及它们的组合;支持行为级、RTL级和带SDF后仿的门级数字电路门级 Verilog和 VHDL仿真;支持高阶的系统级SystemVerilog加SystemC混合仿真,通过无缝集成通用验证方法(UVM)为用户提供快速验证测试台的设置,使验证过程更加高效和可控;提供全面的功能、断言和代码覆盖率测试,可生成多种格式的仿真数据;输入文件可通过加密算法进行保护,确保客户 IP得到充分的安全保护;VeriSim集成概伦电子NanoSpice系列的各种晶体管级电路仿真器,提供完整的混合信号验证解决方案。

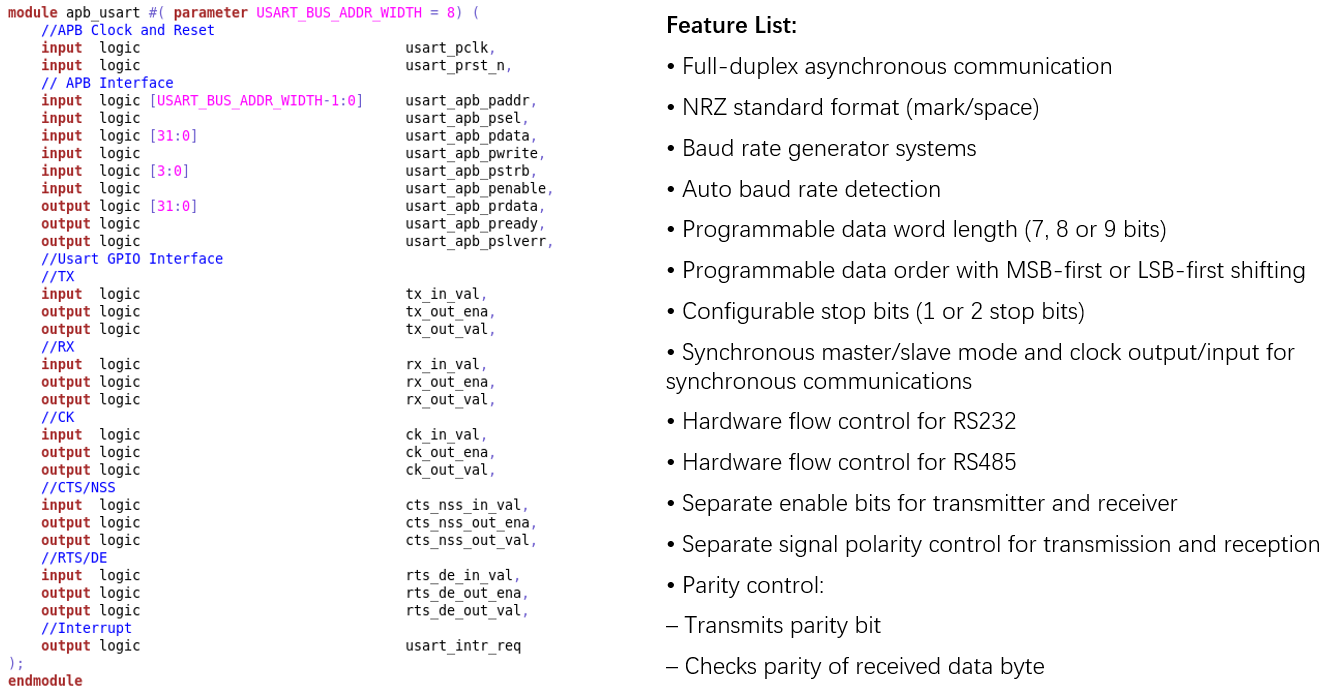

USART(Universal Synchronous/Asynchronous Receiver/Transmitter)是一个全双工通用同步/异步串行收发模块,USART协议从早期的UART开始,经过扩展同步功能以及持续的技术优化与更新,形成了广泛应用于物联网设备,嵌入式系统和微控制器的成熟通信协议。请基于这一标准设计一个USART模块,并基于UVM或PVM方法论搭建验证平台,使用VeriSim仿真器进行功能验证。用Verilog语言实现USART模块的设计,模块接口定义和功能列表如下所示

方案和代码各占15分。用标准的测试平台和测试用例进行测试,每漏掉一个功能点扣1分。

用学员的测试平台跑标准的设计DUT,能正常运行说明平台逻辑正确。方案和代码各占15分。测试点需要覆盖题目要求的所有功能点,包括正常情况和异常情况。遗漏一个测试点扣1分,仿真不通过的用例扣1分。

统一用标准的功能覆盖率定义测试用户的测试用例,并统计功能覆盖率。覆盖率小于60%计0分,100%计20分,以此类推。

从两个指标评判:(1)每仿真1ms所需的CPU时间(总CPU运行时间/仿真时间)。(2)最高内存占用。这两个指标各占10分,分别将学员的数据排序,值越低,得分越高。

完成PVM验证平台,并编译通过计5分,每完成一条测试用例加1分,最多加5分。

软件申请表下载链接

https://kdocs.cn/l/cgm8Gu15YbEe

软件获取方式

1、队伍需要在大赛官网报名概伦电子赛题

2、软件申请表作为邮件附件,通过邮箱发送至useryy2@163.com

邮件命名规则:创芯大赛概伦电子赛题X -学校名称-队伍名称

3、完成以上两个条件的报名队伍,概伦电子将在审核确认后发放软件及账号

4、因软件账号需要自行注册,请加入概伦电子企业命题交流群,以便获取更多概伦电子最新通知。加群方式详见大赛官网概伦电子赛题页面

5、若有其它疑问请联系秘书处微信cpicic-ctri

MeQLab是一款灵活的跨平台建模软件,为器件模型提取提供了完整的解决方案:从S参数测试,大、小信号建模,QA到建模报告自动生成,满足全流程建模应用。该软件支持全面的Compact模型如FinFet、GaN ASM-HEMT,子电路模型, Verilog-A模型, 以及基于子电路的BSIM模型衍生的高压模型的提取。MeqLab内置NanoSPICE仿真器,同时支持链接外部仿真器(如HSPICE、Spectre等),且支持多仿真器的并行仿真验证。该软件集成了丰富的射频建模应用模板,同时开放脚本编程环境,支持灵活的用户自定义设置如去嵌程序、模型自动提参流程设计等应用,满足硅基或者化合物工艺器件建模应用。

任选一类PDSOI或者FDSOI MOSFET器件完成建模,包括器件的直流特性、射频小信号特性以及大信号的谐波功率特性等相关的参数提取,细节如下:

任务1、任选一类SOI器件,简述其结构,工作原理,工艺制备流程,并指出器件特有的效应。(20分)

任务2、基于实测或者TCAD仿真数据,任选一类模型并给出射频小信号等效拓扑结构,完成直流和射频小信号模型参数的提取。(55分)

任务3、完成大信号模型的验证及优化(Pout/PAE vs Pin等)。(15分)

任务4、给出本次完整的建模报告,数据和模型文件,并进行综合性小结。(10分)

任务5、(可选加分项,可累加分数)

赛题二三考核标准会依据建模试题的完整性、创新性、建模精度结合难度系数共同考量。(理论上先进工艺结点引入效应会更多,建模难度也会增加,或特殊工艺的特殊效应)

软件申请表下载链接

https://kdocs.cn/l/cgm8Gu15YbEe

软件获取方式

1、队伍需要在大赛官网报名概伦电子赛题

2、软件申请表作为邮件附件,通过邮箱发送至useryy2@163.com

邮件命名规则:创芯大赛概伦电子赛题X -学校名称-队伍名称

3、完成以上两个条件的报名队伍,概伦电子将在审核确认后发放软件及账号

4、因软件账号需要自行注册,请加入概伦电子企业命题交流群,以便获取更多概伦电子最新通知。加群方式详见大赛官网概伦电子赛题页面

5、若有其它疑问请联系秘书处微信cpicic-ctri

MeQLab是一款灵活的跨平台建模软件,为器件模型提取提供了完整的解决方案:从S参数测试,大、小信号建模,QA到建模报告自动生成,满足全流程建模应用。该软件支持全面的Compact模型如FinFet、GaN ASM-HEMT,子电路模型, Verilog-A模型, 以及基于子电路的BSIM模型衍生的高压模型的提取。MeqLab内置NanoSPICE仿真器,同时支持链接外部仿真器(如HSPICE、Spectre等),且支持多仿真器的并行仿真验证。该软件集成了丰富的射频建模应用模板,同时开放脚本编程环境,支持灵活的用户自定义设置如去嵌程序、模型自动提参流程设计等应用,满足硅基或者化合物工艺器件建模应用。

任选一类器件,完成器件结构、工艺流程解析、建模、参数提取及拟合精度分析。不限定器件类型、制备工艺,例如可以是MOSFET、BJT、diode等器件。

赛题二三考核标准会依据建模试题的完整性、创新性、建模精度结合难度系数共同考量。(理论上先进工艺结点引入效应会更多,建模难度也会增加,或特殊工艺的特殊效应)

软件申请表下载链接

https://kdocs.cn/l/cgm8Gu15YbEe

软件获取方式

1、队伍需要在大赛官网报名概伦电子赛题

2、软件申请表作为邮件附件,通过邮箱发送至useryy2@163.com

邮件命名规则:创芯大赛概伦电子赛题X -学校名称-队伍名称

3、完成以上两个条件的报名队伍,概伦电子将在审核确认后发放软件及账号

4、因软件账号需要自行注册,请加入概伦电子企业命题交流群,以便获取更多概伦电子最新通知。加群方式详见大赛官网概伦电子赛题页面

5、若有其它疑问请联系秘书处微信cpicic-ctri